发布日期:2023/2/7CIS芯片异常

发布单位:iST宜特

CIS芯片的结构较薄、3D堆栈特殊,让您遇到异常点时求助无门吗?

CMOS影像传感器(CMOS Image Sensor,简称CIS)技术的发展,来自于人们对摄影镜头分辨率/画素需求增加,CIS产品能够从早期数十万像素,一路朝亿级像素迈进,端有赖于摩尔定律(Moore’s Law)在半导体微缩工艺地演进,使得讯号处理能力显着提升。然而同时,却也使得这类CIS产品在研发阶段或量产若遇到异常(Defect)现象时,相关失效分析困难度大大提升。

那该如何找到这类型CIS芯片异常 Defect呢?在本期宜特小学堂开始之前,我们要先来认识CIS有哪些类型。

CIS芯片异常

CIS芯片异常

一、认识CIS三大芯片架构

现今CIS芯片架构,可概分为三大类,(一)前照式 (Front Side illumination,简称FSI); (二)背照式 (Back Side illumination,简称BSI);(三) 堆栈式CIS (Stacked CIS):

(一) 前照式(FSI) CIS

为使CIS芯片能符合半导体工艺导入量产,最初期的CIS芯片为前照式 (Front Side illumination,简称FSI) CIS;其感光路径系透过芯片表面进行收光,不过,前照式CIS在效能上的最大致命伤为感光路径会因芯片的感光组件上方金属层干扰,而造成光感应敏度衰减。

(二) 背照式(BSI) CIS

为使CIS芯片能有较佳的光感应敏度,背照式 (Back Side illumination ,简称BSI) CIS技术应运而生。此类型产品的感光路径,系由薄化至数微米后芯片背面进行收光,藉此大幅提升光感应能力。

而BSI CIS的前段工艺与FSI CIS类似,主要差别在于后段芯片对接与薄化制程。BSI CIS的工艺是在如同FSI CIS一般工艺后,会将该CIS芯片正面与Carrier wafer对接。对接后的芯片再针对CIS芯片背面进行Backside grinding制程至数微米厚度以再增进收光效率,即完成BSI CIS。

(三) 堆栈式(Stacked) CIS

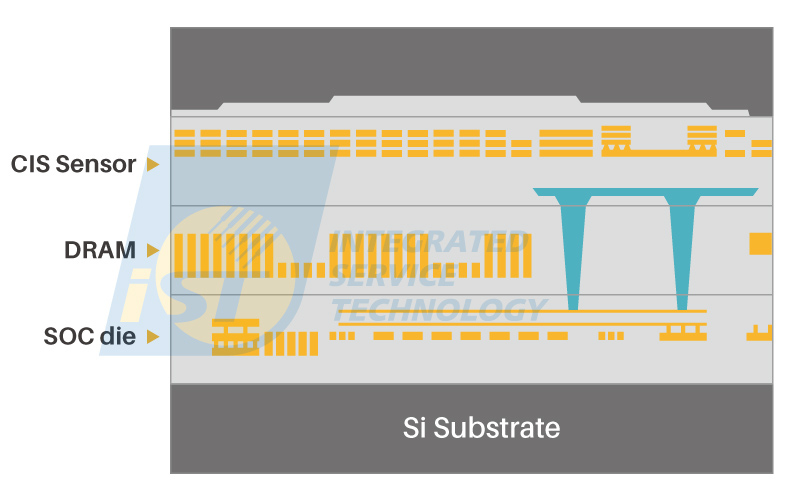

随着智能型手机等消费电子应用的蓬勃发展,人们对于拍摄影像的图像处理功能需求也大幅增加,使制作成本更亲民与芯片效能更能有效提升,利用晶圆级堆栈技术,将较成熟工艺制作的光感测组件 (Sensor Chip) 芯片,与由先进工艺制作、能提供更强大计算能力的特殊应用IC (Application Specific Integrated Circuit,简称ASIC) 芯片、或是再进一步与内存(DRAM)芯片进行晶圆级堆栈后,便可制作出兼具高效能与成本效益的堆栈式CIS (Stacked CIS)芯片(图一)。

二、 如何找堆栈式(Stacked) CIS芯片的异常点(Defect)呢?

介绍完三大类CIS架构,我们就来进入本期宜特小学堂重点-如何找到堆栈式(Stacked) CIS芯片异常 Defect? 由于这类型的CIS芯片结构相对复杂,在进行破坏性分析前,需透过电路专家电路分析或热点(Hot Spot)故障分析,锁定目标、缩小范围在 Stacked CIS芯片中的其一芯片后,针对可疑的失效点/失效层,进行该CIS样品破坏性分析,方可有效地呈现失效点的失效状态以进行进一步的预防修正措施。

接着,我们将分享宜特故障分析实验室,是如何(一)利用电性热点定位;(二)移除非锁定目标之晶粒(Die),并针对锁定目标晶粒(Die)逐层分析;(三)电性量测分析;(四)超音波显微镜(SAT)分析等四大分析手法交互应用,进行Stacked CIS芯片进行失效分析,顺利找到异常点(Defect)。

(一) 透过电性热点定位找故障点(Hot Spot)

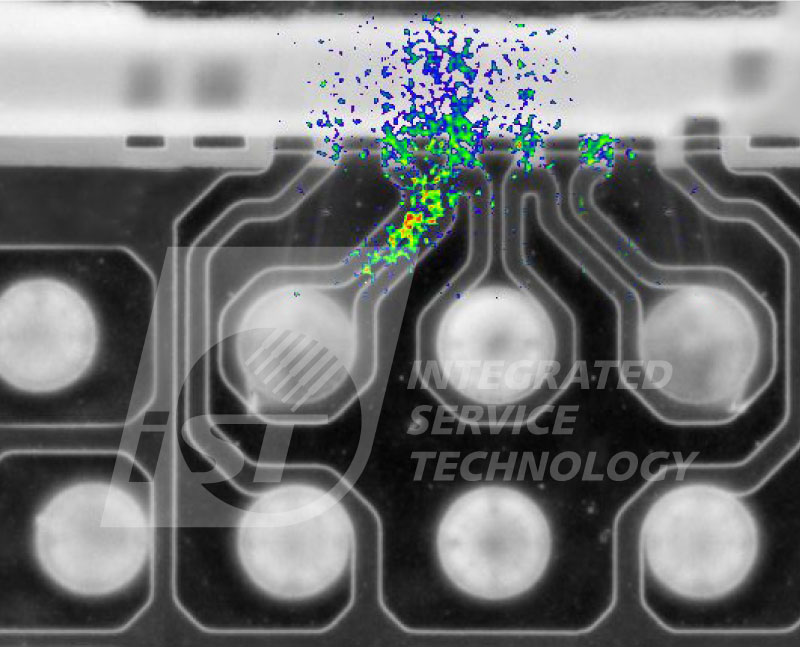

当CIS芯片具有高阻值(High Resistance)、短路(Short)、漏电(Leakage)或是功能失效(Function Failure)等电性失效时,可依据不同的电性失效模式,经由直流通电或上测试板通电,并透过选择适合的电性故障分析(Electrical Failure Analysis,简称EFA)工具来进行电性定位分析,包括激光束电阻异常侦测(Optical Beam Induced Resistance Change,简称OBIRCH)、热辐射异常侦测显微镜(Thermal EMMI)(图二)、砷化镓铟微光显微镜(InGaAs),藉由故障点定位设备找出可能的异常热点(Hot Spot)位置,以利后续的物性故障(Physical Failure Analysis,简称PFA)分析。

● 各设备适合使用的选择时机

设备 OBIRCH Thermal EMMI InGaAs 侦测目标 晶体管/金属层 金属层/ 封装/

印刷电路板晶体管/ 金属层 失效模式 漏电, 短路, 高阻值 漏电, 短路, 高阻值 漏电, 短路, 开路 (二) 移除非锁定目标之晶粒,并针对锁定目标晶粒逐层分析

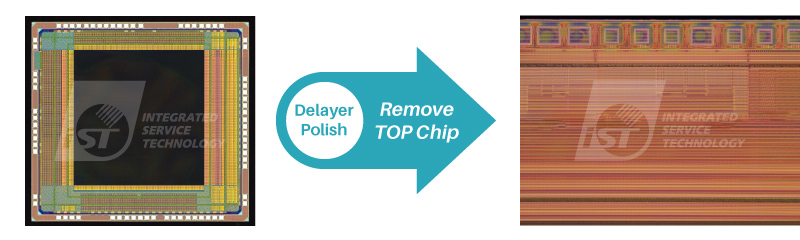

接着,依照上述电性分析缩小可能的异常范围至光感测组件芯片、ASIC或内存芯片区后,根据Stacked CIS芯片堆栈的结构特性,需先将其一侧的硅基材移除,方可进行逐层去除(Layer by layer),或层层检查。

再者,透过宜特开发的独家分析手法,移除不需保留的晶粒结构,进而露出目标晶粒之最上层金属层(图三)。接着,透过逐层去除(Layer by layer),最终在金属层第一层(Metal 1)找到烧毁现象的异常点(defect)(图四)。

(三)电性量测分析:导电性原子力显微镜(Conductive Atomic Force Microscopy, C-AFM)与奈米探针系统(Nano-prober)的应用

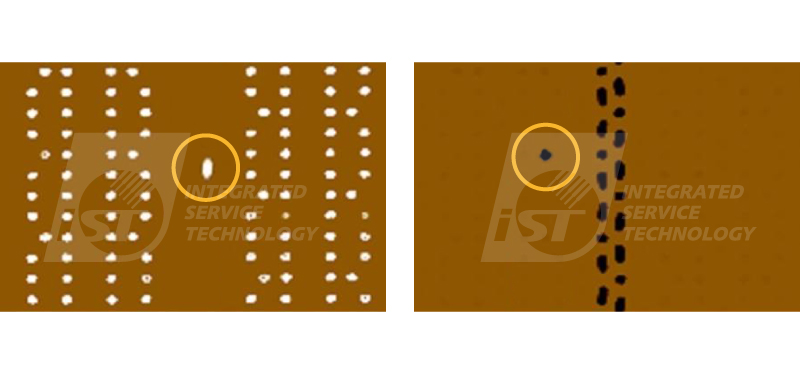

当逐层去除(Layer by Layer)过程当中,除利用电子显微镜(SEM) 于故障点区域进行电压对比 (Voltage Contrast, 简称VC)的电性确认与金属导线型态观察外,亦可搭配导电原子力显微镜(Conductive Atomic Force Microscopy简称C-AFM)快速扫描该异常区域,以获得该区域电流分布图(Current map)(图五),并量测该接点对硅基板(Si Substrate)的电性表现,进而确认该区域是否有漏电/开路等电性异常问题。

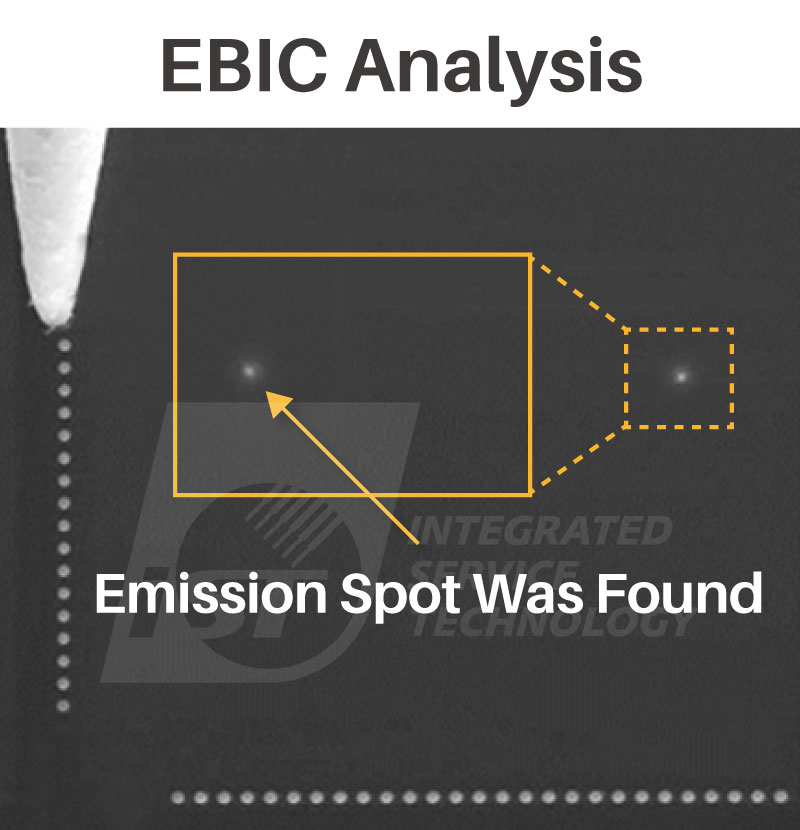

在完成C-AFM分析后,若有相关疑似异常路径需要进一步进行电性量测与定位,可使用奈米探针电性量测(Nano-Prober)进行更精准的异常点定位分析,包括电子束感应电流(Electron Beam Induced Current,简称 EBIC、电子束吸收电流(Electron Beam Absorbed Current,简称 EBAC)、与电子束感应阻抗侦测(Electron Beam Induced Resistance Change,简称 EBIRCH)等定位法(深入阅读: 名针探精准定位 让奈米电性量测找出缺陷)。而Nano-Prober亦可针对晶体管进行电性量测,如Vt、 IdVg、IdVd等基本参数获取(图六)。

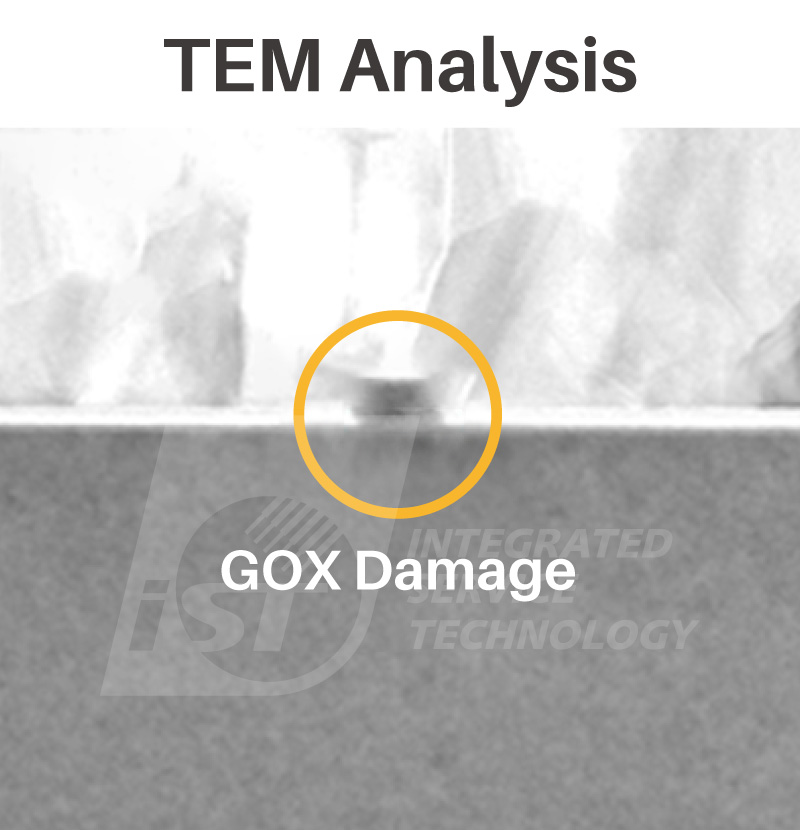

当透过上述分析手法精准找到异常点后,亦可再透过双束聚焦离子束(Dual-beam FIB,简称DB-FIB)或是穿透式电子显微镜(Transmission Electron Microscopy,简称TEM)来对异常点进行结构确认,以厘清失效原因(图七)。

(四) 超音波显微镜 (Scanning Acoustic Tomography,简称SAT)分析:于背照式(BSI)/堆栈式(Stacked) CIS晶圆对接制程的应用

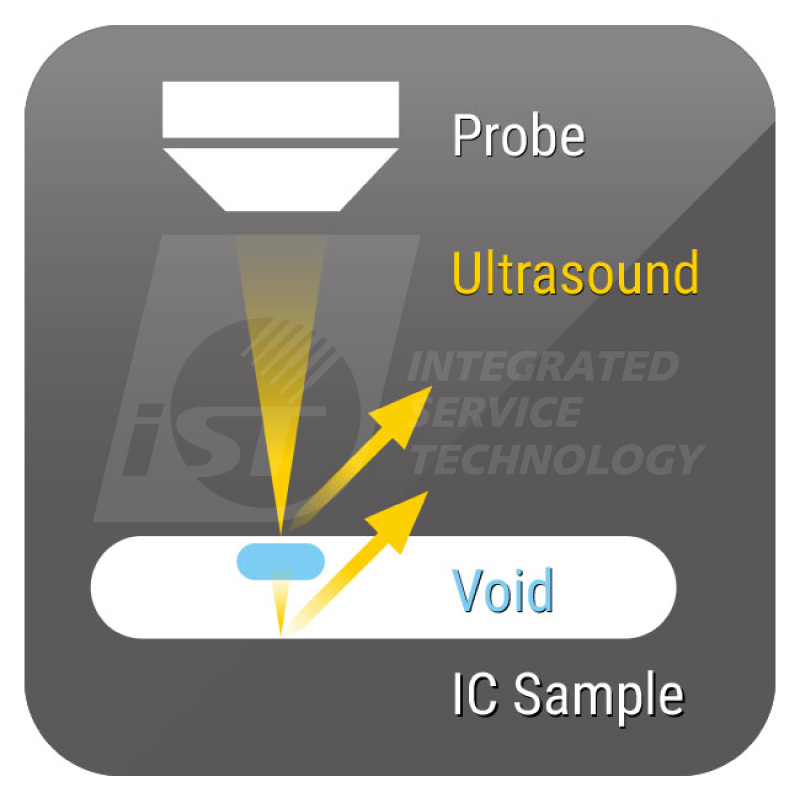

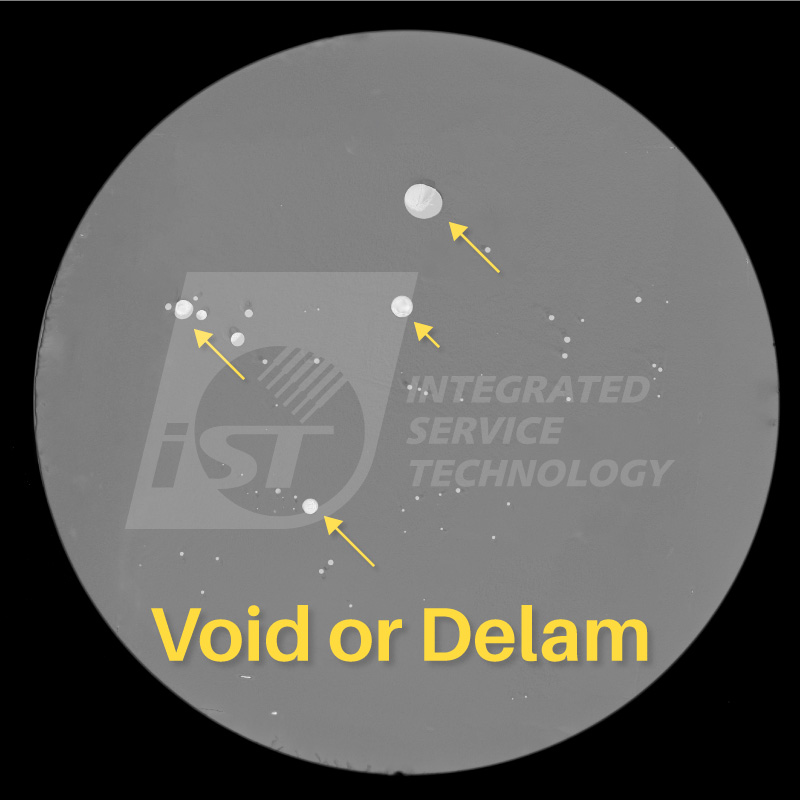

超音波显微镜(SAT)为藉由超音波于不同密度材料反射速率及回传能量不同的特性来进行分析,当超音波遇到不同材料的接合接口时,讯号会部分反射及部分穿透,但当超音波遇到空气(空隙)接口时,讯号则会100%反射,机台就会接收这些讯号组成影像(图八)。

在背照式(BSI)与堆栈式(Stacked) CIS制程中晶圆与晶圆对接(bonding)制程中,SAT可作为侦测晶圆与晶圆之间接合不良造成存在空隙的重要利器(图九)。

随着半导体堆栈技术的蓬勃发展与人们对影像传感器在消费性电子、车用电子、安控系统等应用的功能需求大幅度增加,堆栈式CIS产品将逐渐成为未来CIS产品主流,除了前照式与背照式CIS的故障分析手法已建置完备外,宜特科技故障分析实验室也能够根据客户所需,无论是晶圆级对接的制程稳定度分析,或是堆栈式(Stacked) CIS故障分析,都可以透过宜特实验室丰富的分析手法与一站式整合服务,协助您精准地分析、加速产品开发、改善产品质量。

本文与各位长久以来支持宜特的您,分享经验,若您想要更进一步了解细节,欢迎洽询+886-3-579-9909 分机6612 李先生│Email: IST_FA_IAD@istgroup.com;marketing_tw@istgroup.com