5G

拒当 5G 时代的局外人: 相关封装测试项目, 你准备好了吗?

针对5G装置的先进封装需求,其可分为终端应用以及云端应用两个层面来探讨:

终端装置的高阶封装需求

终端装置包含应用在手机以及笔记本电脑(NB)的部分,如以5G手机为例,其应用讲求轻薄短小、传输快速,且整体效能取决于核心的应用处理器AP(Application Processor) 芯片。当然随着5G高频波段的使用,负责传输讯号的天线设计也须随之改变。

以下将针对应用处理器与天线做进一步的说明:

1. 5G手机的应用处理器(Application Processor,AP)

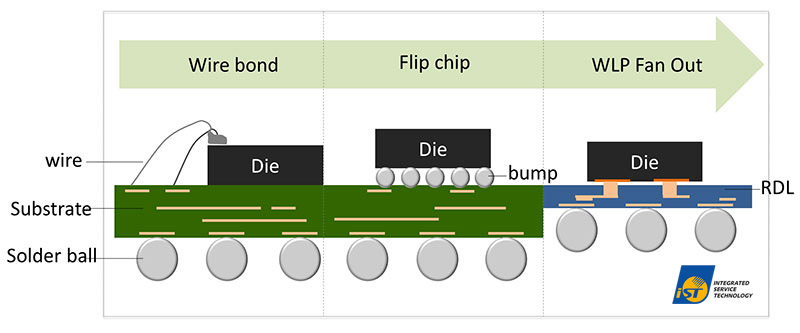

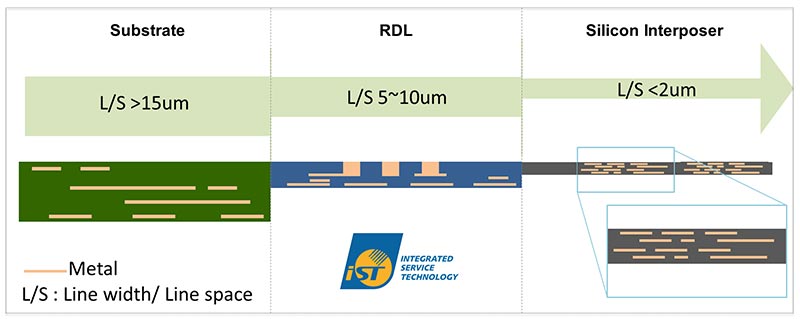

AP性能的提升除了晶圆工艺的微缩外,就是依靠封装技术的协助。其形式主要是以POP(Package on package)封装为主,藉由POP的方式来堆栈DRAM能有效提升芯片间的传输效率并减少所需的体积。其连接方式从传统的打线(wire bonding)、覆晶(Filp chip)一路演进到目前的扇出型(Fan-out)封装。扇出型封装主要是利用RDL布线减少载板(substrate)的使用,如下示意图

藉此减少载板的使用,间接达到效能提升、改善散热、降低产品尺寸及成本的目的,因此在AP的IC选择上,多以Fan out POP(Package on package)封装型式为主。

2. 天线

随着5G将高频毫米波频段导入商用,使得5G讯号从1GHz以下,延伸至超过30GHz,装置对于天线的需求更胜以往,使得天线尺寸、路径损耗以及讯号的完整性必须被加以考虑

- 天线尺寸:由于天线体积取决于频率,随着更高频波段毫米波(mmWave)的使用,天线将能有效的缩小尺寸至毫米等级。

- 信号完整性:透过增加天线数量进行发送及接受讯号,能使得数据传输的速度更快,更精确

- 路径损耗:高频波段穿透性强,但穿透所造成的能量耗损以及干扰会使得有效传输距离变短

因此在天线数量激增、可用面积维持不变的情况,天线封装(Antenna in Package,AiP)封装型式,则成为目前厂商的最佳解决方案,AiP主要采SiP(System in Package)或PoP的结构将RF芯片置入封装以达到缩小体积、减少传输的距离以降低讯号传输时造成的耗损的目的。结构上可利用RF芯片的位置将结构区分成两种,一种是包含在substrate内部的结构,另一种则是将RFIC置于substrate外侧的结构。

云端装置的高阶封装需求

技术挑战

1. 热膨胀系数不匹配(CTE mismatch)

不同的材料具有不同的热膨胀系数(coefficients of thermal expansion,CTE),随着温度的变化使得材料的膨胀状况不一,因此会产生材料应力(material stress)。由于5G封装内堆栈了多种异质芯片,应力释放的过程将更容易导致裂痕或脱层的现象并影响芯片的运作。

「热」永远是产品可靠度的第一杀手,特别是同一封装中纳入不同芯片的温度耐受度不一,芯片外部温度、系统温度也会产生影响。

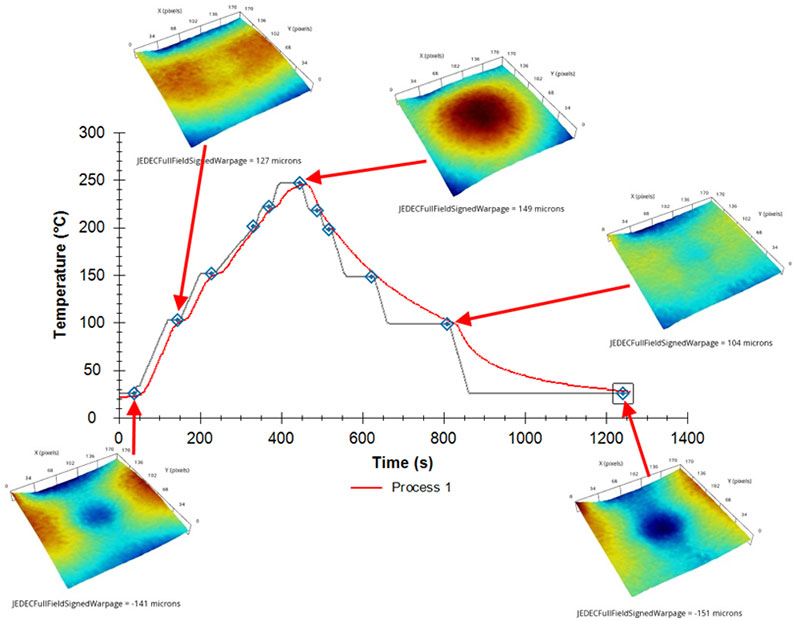

2. 翘曲(Warpage)

由于5G先进封装异质整合芯片堆栈较以往复杂,且封装体积有扩大的趋势,容易导致substrate严重的翘曲(Warpage)。特别是在进行表面黏着技术(SMT)时,因高温使得翘曲更加严重导致无法顺利焊接于PCB板上。除此之外warpage也可能导致双球(Head in Pillow)的现象,进而造成可靠度测试早夭的问题。

3. 其他

高功率、高效能的产品主要是利用2.5DIC、3DIC封装,因此需考虑散热及warpage问题,通常会搭配散热盖(heat sink)的设计来同步解决问题,但因其重量较重,在SMT过程中容易将锡球压扁导致短路(bridge)等问题。

5G先进封装芯片验证分析

基于5G先进封装芯片的特性,所以在研发设计时间,包括先进封装芯片翘曲的程度、异质材料整合的材料分析、在锡球上的表面黏着(SMT)状况,以及温度变化下,是否对于锡球、硅中介层接合有所影响等,都需要进行细部验证。

1. 严重翘曲导致SMT失效、测试问题

先进封装产品内部设计复杂度提高、尺寸的扩大,导致产品翘曲程度变严重,其结果会影响SMT上件的困难度以及测试socket接触不良等问题

针对此问题,宜特备有量测翘曲的设备(Shadow moire),可仿回流焊(reflow)过程中组件与PCB 翘曲的程度,藉此调整SMT参数设定,确保SMT过程中有良好的焊接质量。

2. CTE mismatch验证

组件在长期运作的状况下,因环境温湿度的改变,材料交界处常因CTE mismatch而产生内应力,进而造成脱层及裂影响组件的运作。可藉由进行环境可靠度的测试,包括uHAST、TCT、Multi-reflow等模拟实际使用的状况,以确保未来在变更材料、改变设计的状况下,组件依旧能良好的运作。

对此宜特提供可靠性测试规范的咨询,以及失效后一连串分析的服务,以协助客户厘清组件异常的可能原因

3. 先进封装结构复杂,难以用常规手法检测

封装结构的改变,导致进行可靠性验证后,针对脱层等无法被电测出的异常难以用常规的手法(2D x-ray ,SAT ,FIB ,etc)直接进行检测。对此宜特可针对不同的封装结构,提供完整的建议,例如2.5D IC封装进行reflow后确认散热膏是否有脱层等。