发布日期:2019/03/15

发布单位:iST宜特

随半导体产业朝更先进工艺 发展之际,宜特电路修补技术(IC Circuit Edit)检测技术再突破!宜特今(3/15)宣布,宜特通过先进工艺 客户肯定,IC芯片背面(Back-side,简称晶背)FIB电路修补技术达7奈米(nm)工艺 。

宜特针对IC设计业者为何须进行电路修补进行说明。由于即使电路仿真软件不断地提升演进,仍难以100%来确保芯片的设计及布局正确性,一旦发现电路瑕疵只能再次进行光罩改版;然而光罩价格不斐,且重新下光罩后,等待修补过后的芯片时间通常超过一个月。因此,多数IC设计业者,会选择进行IC电路修补,只需几个小时内即可完成修补,确保电路设计符合预期,并降低时间及金钱的成本耗损。

宜特表示,随着摩尔定律,半导体工艺 从1微米(um)、0.5微米(um)、0.13微米(um)不断微缩到奈米(nm)等级,如此先进工艺 的电路修补,考验FIB实验室的技术发展及应用能力。特别当工艺 来到16奈米(nm)以下的工艺 ,包装型式多数为覆晶技术(Flip Chip),因此FIB电路修补就必须从晶背来执行,整体困难度也随之增加。

宜特进一步指出,7奈米(nm)先进工艺 的晶背电路修补,有两个挑战。第一,晶体管密度倍增:每平方毫米密度约是16nm工艺 的3.5倍,要穿越遍布于底层的晶体管进行修补困难度将大幅度提升;第二,薄且小的间隙:7奈米(nm)工艺 的金属与介电层的间隙、宽度、厚度,多为40奈米(nm)或以下,面对薄且小的工艺 ,如何精准定位目标、清楚辨识电路及避免过度曝露金属,更是修补技术能力重要关键。

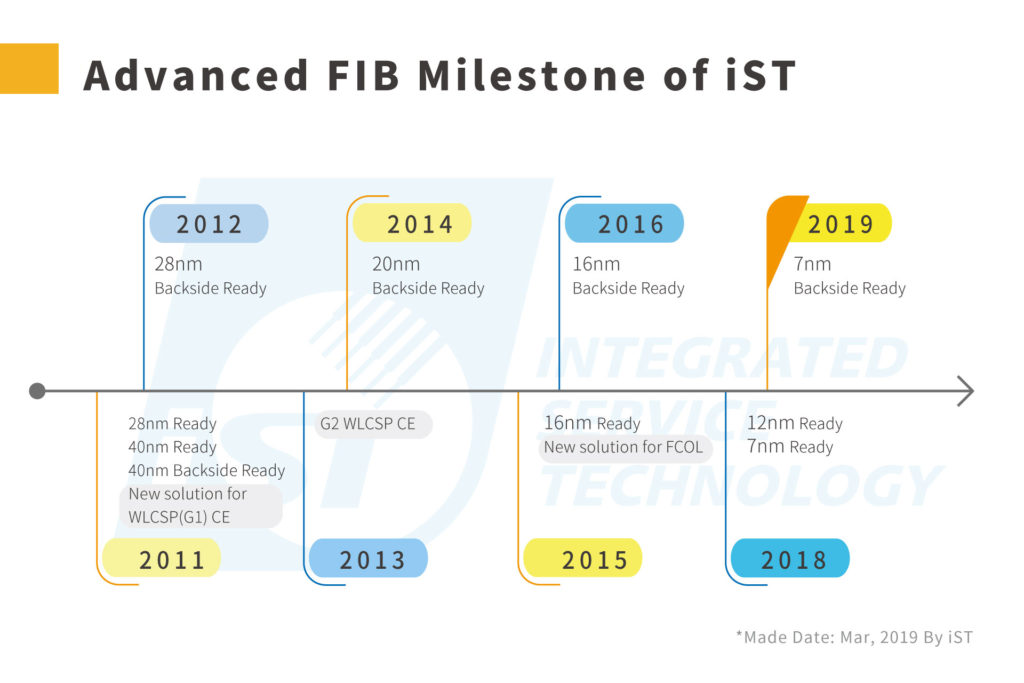

宜特表示,宜特1994年成立,从IC芯片的FIB电路修补起家,2011年即提供40/28奈米(nm)先进工艺 电路修补技术,2015年时完成20/16奈米(nm)芯片正面的电路修补技术,并于2016年挑战完成16奈米(nm)的IC 晶背(back-side)FIB电路修补技术。2018年完成12奈米(nm)修补。

今年,宜特FIB电路修补技术再突破,成功完成7奈米(nm)工艺 的back-side电路修补,协助先进工艺 芯片设计业者在电路验证、侦错、失效分析上更直接、灵活且快速的选择,加速产品上市时间(Time-To-Market)。

图说:宜特结合子公司创量科技(旧名:标准科技),可提供从晶圆工艺处理一路到后段测试与DPS一站式解决方案。

关于宜特科技

始创于1994年,iST宜特从 IC 线路除错及修改起家,逐年拓展新服务,包括故障分析、可靠度验证、材料分析等,建构完整验证与分析工程平台与全方位服务。客群囊括电子产业上游 IC 设计至中下游成品端,并建置车用电子验证平台、高速传输讯号测试。宜特秉持着提供客户完整解决方案的宗旨,从验证领域,跨入「晶圆后端工艺整合」量产服务。更多讯息请上官网 http://www.istgroup.com

媒体联络人

发言人

财务长 林榆桑

+886-3-579-9909 Ext.1888

ir@istgroup.com

代理发言人

品牌企划室 邱钰婷

+886-3-579-9909 Ext.1068

Marketing_tw@istgroup.com