发布日期:2023/10/17薄膜硬度

发布单位:iST宜特

解决先进封装技术中不同材料机械特性的问题,奈米压痕与刮痕测试是关键,但究竟该如何搭配SEM&TEM 以找出故障点呢?

薄膜硬度

在半导体集成电路朝向尺寸微小化和功能极大化的发展方向上,先进封装技术已成为提高芯片性能的重要途径之一。然而,为了达到垂直整合的目的,多层薄膜堆栈结构已被大量地运用在制程当中。由于不同材料之间的机械特性不匹配,以及制程中产生的热机械应力,导致的各种失效模式亦接踵而来。为了克服这些瓶颈,对于材料机械特性的掌握变得至关重要,在微米及奈米尺度的世界中,「奈米压痕测试仪」及「奈米刮痕测试仪」为两个重要的分析工具。除了可用来分析材料的机械特性,以及多层结构中的附着能力,亦可作为区域化应力的工具,搭配后续影像分析技术,如扫描式电子显微镜(SEM)、双束聚焦离子束 (Dual Beam FIB)或穿透式电子显微镜(TEM)可更进一步地分析内部结构变化,找出造成故障的脆弱点位置。本期宜特小学堂与安东帕公司合作,将针对奈米压痕及奈米刮痕的测试原理及相关应用进行说明。

薄膜硬度

薄膜硬度

一、奈米压痕和刮痕测试仪的原理

奈米压痕测试法及刮痕测试法,为两种广泛用于研究材料微机械特性的技术。利用此二种方法,可助于了解材料于微米及奈米尺度下,因应力所产生变形或破坏的机制,与传统测试方法(如维氏或洛氏硬度等)相比,能够提供更多特征参数而非仅仅单一硬度值(延伸阅读: 异质整合当道 材料接合应力强度备受瞩目)。

奈米压痕测试仪,具有精密的应力和深度传感器,可精准控制压头进行加载与卸除过程,并同时记录载荷及压入深度,进而得到与压痕深度相关的各项材料参数,如代表材料抵抗永久变形能力的「压痕硬度 (Hardness,简称HIT)」、用来描述材料弹性的「弹性模量 (Elastic modulus,简称EIT) 」以及材料于固定荷载下持续变形的行为「蠕变特性(Creep,简称CIT) 」等。薄膜硬度

而刮痕试验仪,则用来测量薄膜与基材间或是薄膜本身的结合力,藉由逐渐线性地增加施加于钻石刮头上的力量,于材料表面上产生出剪切力。当薄膜与基材本身的机械性质不同时,在临界负载(Critical Load, Lc)下会产生附着破坏。此临界负载为一项良好的量化参数,可用来代表薄膜的附着能力。在同一刮痕过程中,拥有较大的临界负载的材料具有较佳的附着能力,能够更好地抵抗后续制程中的热应力冲击。

二、奈米压痕和刮痕测试仪的四大应用

(一)利用奈米刮痕探讨多层膜的脱层现象

为了实现3D IC封装技术,半导体组件的结构朝向高度多层化发展-将各种具有不同特性的薄膜材料堆栈在一起。然而,当多层结构在受到不同制程中带来的热及机械应力后,因薄膜/薄膜或是基材/薄膜间机械特性不匹配(如热膨胀系数、杨氏模数或蒲松氏比等)而导致「界面剥离 (interfacial delamination)」现象的发生不断地出现于制程当中,为目前常见导致组件失效的原因之一。

为了改善此问题,掌握材料间的附着能力,以及了解结构在外部应力下的行为变得至关重要。奈米刮痕测试仪是一个很理想的分析方式,除了可用来量化界面剥离作用力,亦可施加外部应力,模拟材料因外部应力而失效的过程。此外,于界面剥离发生后,结合扫描式电子显微镜(SEM)、双束聚焦离子束 (Dual Beam FIB)或穿透式电子显微镜(TEM)可更进一步地分析多层内部结构变化,找出结构中的脆弱处。

以图二Si/SiO2(SiN)/TiN/W多层结构为例[1],利用直径为2 微米的钻石刮头,以 2 mN/s的正向力加载速度,分别于两个不同多层结构样品表面创造出刮痕(如图二)。由刮痕测试仪分析数据可知,样品A及样品B的临界负载分别为 7 mN及 15 mN。代表样品 B具有较佳的抗外应力能力。此外,结合穿透式电子显微镜(TEM)及X射线能谱 (EDS)的成份分布(mapping)分析显示,此二结构发生界面剥离的位置位于 SiO2/TiN 及SiN/TiN界面。

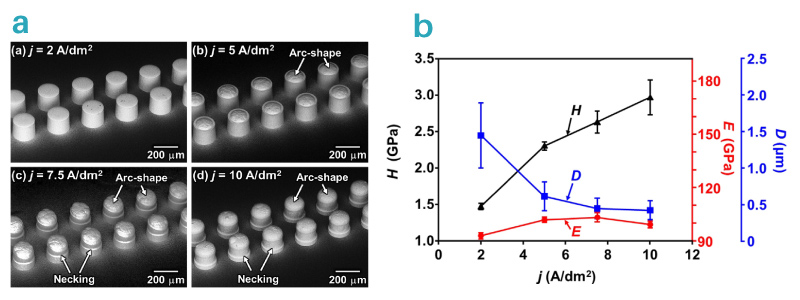

(二)铜柱凸块 (Cu pillar bump)的机械特性分析

为了满足终端产品轻薄短小的需求,芯片讯号处理输入输出需求数量不断增加,这意味着芯片封装中的引线节点数密度需要提高,而用于链接集成电路芯片与基板的凸块 (Bump)间距则需不断缩小。铜材料因具备良好的低电阻、低电感、低热阻,以及抗电子迁移能力等特性,铜柱凸块(Cu Pillar Bump)成为实现小间距的优异选择。

然而,当凸块间距缩小至10微米左右时,许多的问题相继出现[2]。举例而言,铜柱凸块结构在经过回焊制程(Reflow Process),因热应力而导致「桥接失效(Bridge Failure)」现象为一待克服的议题。

为了解决这些问题,我们可以使用搭载显微镜头的奈米压痕测试仪,于特定的铜柱位置进行压痕实验,已获得不同区域的机械特性分析,从而优化制程参数。图三为利用高速电镀方式制备的铜柱凸块[3],搭配不同的制程方式以及奈米压痕实验,可掌握电镀制程中电通量对于铜柱机械特性的影响。由图三(b)可知,铜柱的硬度与电镀制程中施加的电通量呈现正相关。

(三)底部填充材与凸块间机械特性匹配的分析

于IC覆晶(Flip Chip)封装制程中,会于凸块间填入底部填充材料(Underfill)来强化芯片的机械稳定性及提高整体可靠性。Underfill主要为高分子材料,其杨氏模量及热膨胀系数,与周围的铜柱凸块以及底下的硅基材[4]存在显著差异,由于机械特性的不匹配,芯片在后续高温高湿可靠度的测试中,可能出现各种故障模式,例如裂纹产生、基板分离、空洞。

为了找出这些故障的主要原因,解析结构中不同位置机械特性的差异就显得尤其重要。近年来,奈米压痕测试仪已广泛地被用来量测结构中不同位置的机械特性。图四(a)为填充完underfill结构的剖面图,利用奈米压痕搭载的光学显微镜可选定三个不同的区域进行分析,此三个区域包含了铜柱凸块、底部填充材、后段制程芯片以及硅芯片。薄膜硬度

由图四(b)结果可知,杨氏模量的不均匀分布显示underfill中还存在其他填充物。图四(c)则可以看到铜柱凸块与芯片间界面的弹性模量分布。于特定位置进行压痕测试分析,可得到硅晶圆、铜柱凸块以及underfill的杨氏模量。如图四(d)显示,其分别为169 ± 3 GPa, 119±6 GPa and 9 ± 3 GPa。[4]由此结果可发现,由于模量的显著差异,增加了此结构因后续制程产生的失效风险。

因此搭配压痕测试仪的结果,可有效寻找较适化的制程参数,或透过更改不同特性的材料,来避免因机械特性不匹配造成产品的故障。

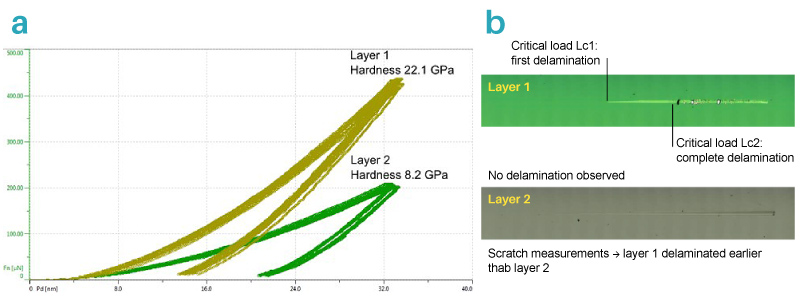

(四)钝化保护层硬度与附着能力相关性的分析

在晶圆级尺寸封装(Wafer Level Package)结构中,为了于基板上制作出如晶体管的主动装置,利用各种不同的沉积方法于底材上方堆栈出金属层、包含线路重布的金属线层(RDL)、用以连接电路的金属垫(Pad)以及钝化保护层(Passivation layers)。[5] 钝化保护层的主要作用是保护底下结构不致受到外在环境的污染或损伤。不同的沉积方式或制程条件,对于钝化保护层的机械特性及与底材的附着能力有显著的影响。结合奈米压痕测试仪及刮痕测试仪量测结果,不仅能够找出薄膜机械特性及附着能力的关系,亦可加速制程优化及保护层材料的筛选,从而加快后续的开发流程。薄膜硬度

以氮化硅(SiNx)薄膜为例,图五(a)为利用两种不同制程方式于硅晶圆表面沉积出厚度约为300 奈米薄膜的载荷-压深曲线。由结果可知,Layer 1的硬度高于Layer 2。而进一步地利用刮痕测试仪分析其附着能力时却发现,Layer 1在较小的载荷下就观察到界面剥离现象,相反地,于同一刮程下,Layer 2并未观察到界面剥离现象 ,此结果表示Layer 2的附着能力大于Layer 1。

若比较压痕测试出来的结果,可有趣地发现,虽然Layer 1拥有较高的硬度,但附着能力并未较佳。由此结果可知,薄膜的机械特性和附着能力的展现并非都呈现正相关性,因此须结合二者全方面的探讨才能找出最适化的材料特性。

近年来,随着封装技术不断的演进,传统单一的大面积素材已不符合3D复杂结构的应用,微小空间中不同尺寸芯片的结合、并列或堆栈的趋势则日益明显,但如此微小结构中的异质材料,在封装后受到机械应力互相影响的因子也变得更加复杂,因此,除了必须具备精密的微区机械特性量测能力之外,结合影像判断的SEM、DB-FIB及TEM电子显微镜也成为必要的分析工具。在未来IC的先进封装技术开发中,宜特科技将持续不断地与所有合作的客户共同努力,研发出更有效率的下一代芯片,使得我们未来生活更多采多姿。

本文与长久以来支持宜特的您分享。若您有相关需求,或是对相关知识想要更进一步了解细节,欢迎洽询 +886-3-579-9909 分机 6176 江先生 / Email: web_sa@istgroup.com;marketing_tw@istgroup.com。

参考文献:

[1] Jin-Hoom Kim, Hye-Jun Kil, Sangjun Lee, Jinwoo Park, and Jin-Woo Park. ACS Omega 2022, 7, 25219−25228.

[2] https://technews.tw/2022/07/29/ma-tek-package-design-hybrid-bonding/

[3] Pei-Tzu Lee, Chih-Hao Chang, Cheng-Yu Lee et al. Materials & Design 206 (2021) 109830 “High-speed electrodeposition for Cu pillar fabrication and Cu pillar adhesion to an Ajinomoto build-up film (ABF)”

[4] Thesis with the title “Micromechanical indentation study of stress related effects in transistor channels” by Simon Schlipf

[5] 中华民国专利,申请案号:102121292

![图(a)多层结构示意图及说明。(b)不同样品界面刮痕剥离影像图。(c) 多层结构Si/SiO2/TiN/W样品A的TEM及EDS mapping分析结果。(d) Si/SiN/TiN/W 样品 B的 TEM及EDS mapping分析结果。[1]](https://cn.istgroup.com/wp-content/uploads/2023/10/tech_20231017-02-Thin-film-adhesion-hardness-1.jpg)