發佈日期:2024/9/5 硅光子芯片

發佈單位:iST宜特

2020年Intel就已提出硅光子将是先进封装发展关键,如今四年过去,硅光子技术已真正成为半导体产业的关键研发核心,并预计两年后将完成整合正式上阵。面对这次的「电」去「光」来新革命,您准备好了吗?

硅光子芯片

随着半导体集成电路技术的不断发展,我们见证了摩尔定律的演进,组件尺寸的微缩和新材料的应用,都是为了提高单位面积内的组件数量,以加速IC的指令周期,同时改善散热效能和节省能源。然而,随着尺寸的微缩接近物理极限,工艺技术面临挑战,良率问题也随之浮现。

因应这一挑战,专家开始探索将不同功能的IC集合成单一芯片、采用3D堆栈封装技术等新途径,但这些技术的核心仍然是用金属线连接各个组件。自从芯片问世以来,「电子」一直是主要的讯号传输媒介,它的传输速度直接决定了芯片的性能。近年来高效能运算(HPC)、人工智能(AI)、云端数据等需求爆炸性成长,如何能突破限制实现更高效能的传输呢?于是大家把目光转向了「光子」,藉由更快速的「光子」引入,是否可以加快组件的运作呢?

硅光子芯片

光通讯运用的「光纤」系统,能于世界各地以每秒数万亿bit的速度传送数据,1968年贝尔实验室工程师很早就想到了。到了21世纪初发现光子技术不仅能在国与国之间做数据的传递,亦可在数据中心甚至是CPU之间,乃至于在芯片与芯片之间做数据传输。之所以采用「光」是因为玻璃(SiO2)对于光来说是透明的,不会发生干扰的现象,基本上,可以透过在SiO2中,结合能够传递电磁波的光波导(Waveguide)通路来高速地传输数据。

而硅(Si)材料的折射率(Refractive index)对比在红外线的波长下高达3.5,这也意味着,它比许多其他光学中所用的材料,更能有效地控制光的弯折或减速。一般光学传输的波长是1.3和1.55微米,在这两个波段下硅材料不会吸收光线,因此光线能够直接穿透硅材料。这种兼容性使硅基设备能够长距离传输大量数据,不会明显失去讯号。

因此,硅光子技术透过原本CMOS硅(Si)的成熟技术,结合光子组件工艺,可以使处理器核心之间的数据传输速度提高数百倍以上,且耗能更低;除了前面提到高效运算跟人工智能需求不断增加,光学雷达、生医感测也非常适合使用光子组件,世界前几大IC制造商都相继发表硅光子是未来IC技术的关键及趋势,本期宜特小学堂与大家分享相关文献,了解硅光子组件组成与决定效能的关键。

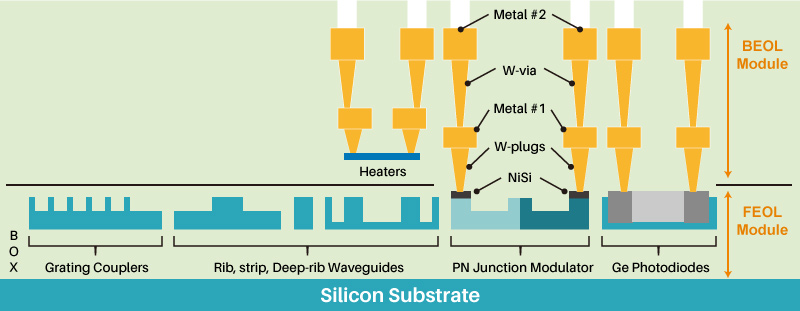

一、 硅光子组件组成,材料以「锗」为首选

硅光子组件的基本组成是使用能将「光」转换成「电」讯号的p-i-n diode(PIN二极管)光电侦测器,加上传输讯号的光波导(Wave guide)与电讯号转成光子的调变器(Modulator)、耦合器(Coupler)等所组合成的一个单芯片,断面的结构大致如图一所示。

其中最关键的制造技术即在图一最右侧PIN二极管,首选的半导体材料为锗(Ge),因为锗具有准直接能隙(Quasi-Direct band gap)且仅有0.8eV小于光子能量,另外对于光的吸收系数很高更适合用于光电侦测器,是一种非常好的取代材料。

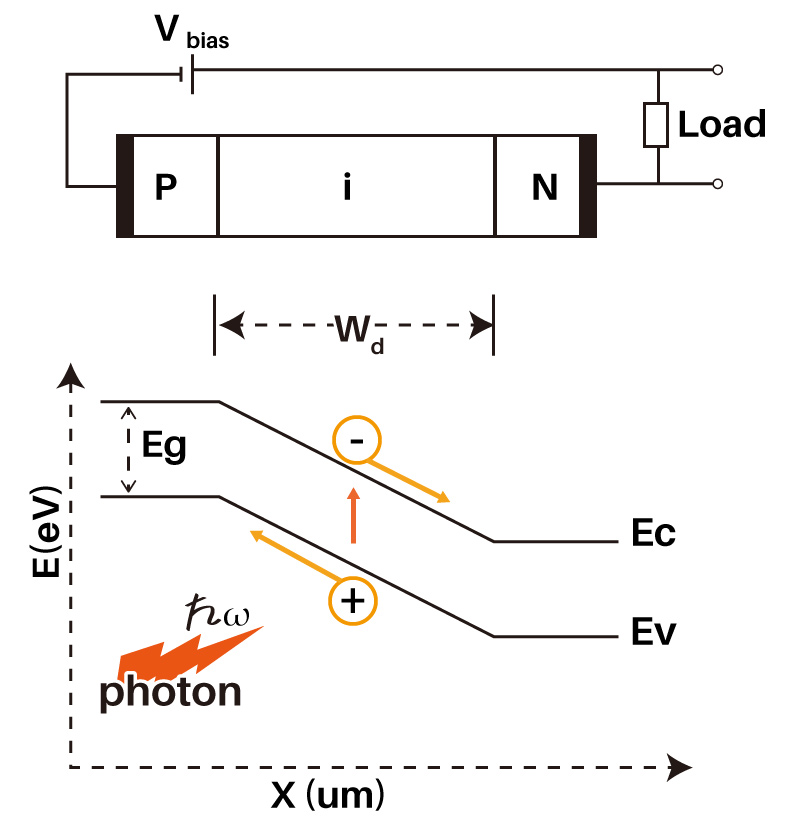

PIN是由一组高掺杂P (p+)型区和N (n+)型区之间夹着一层本质(Intrinsic)区所组成。在负偏压下二极管的空乏宽度 (Wd)会扩展至整个本质层。如图二下能带结构所示,当入射到本质层中的光子被吸收后,于导电和价电带间产生电子–电洞对的漂移而形成电流。在硅光子组件的研发中最重要的方向,就是在不影响常规CMOS组件的特性下透过调整光电侦测器PIN的工艺,且能使效能与带宽达到优化。

二、 如何辨别Ge-PIN的质量?

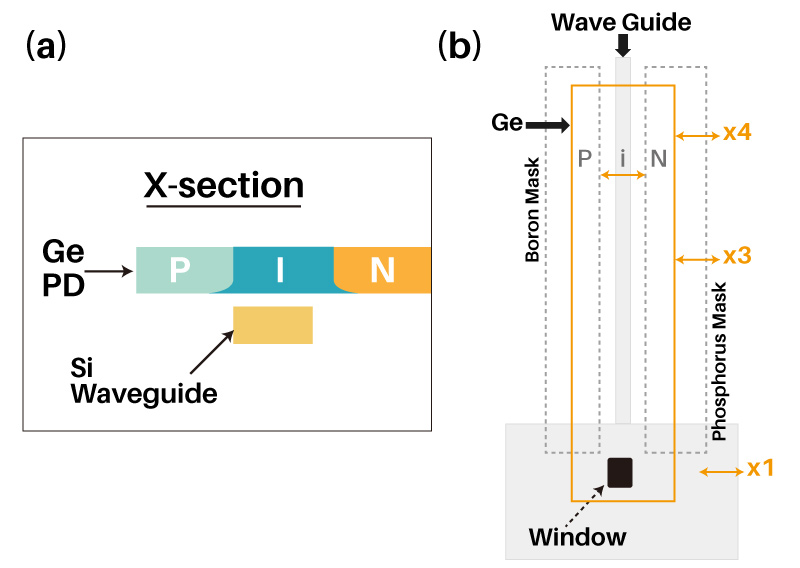

先以图三简单的说明一颗单芯片的设计,Ge-PIN光电侦测器与Si-光波导的相对位置,(a)图为剖面结构示意图,光波导位于本质层下方,(b)图为正面Layout。

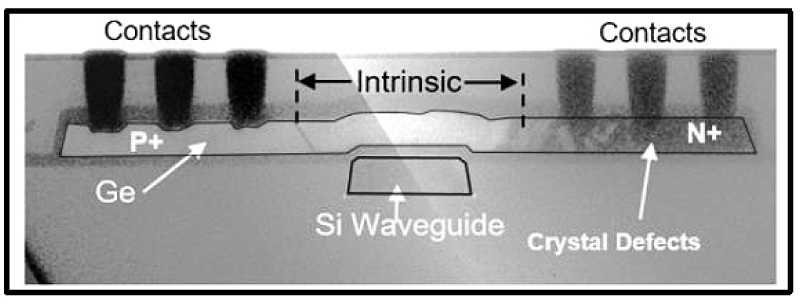

因为Ge-PIN的质量差异会影响到侦测器的光电效能,Ge的磊晶工艺与Si之间会有晶格不匹配与离子植入产生的差排缺陷等影响质量,图四是Ge-PIN藉由穿透式电子显微镜(TEM)的观察,可以明显看出在本质层(Intrinsic)与P区均呈现亮区,代表没有明显缺陷,反观在右侧的N区则呈现暗灰色,这应该是源自于离子植入工艺所产生的晶格缺陷。(延伸阅读:破解半导体差排轨迹 TEM技术找出芯片漏电真因)

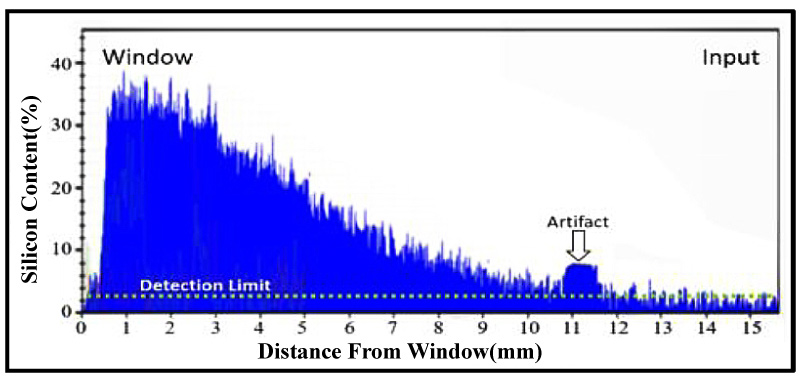

此外,藉由EDS来分析波导中的Si是否有朝向Ge-PIN扩散的情形。图五为Ge层中沿着波导方向Si的含量分布。Si 摩尔百分比从接触窗(Window)最高约35%,向输入侧减少至低于EDS检测极限的2%,约是在11mm的位置处,表示发生明显的扩散现象。

三、 如何观察影响光电侦测器效能空乏区宽度的大小?

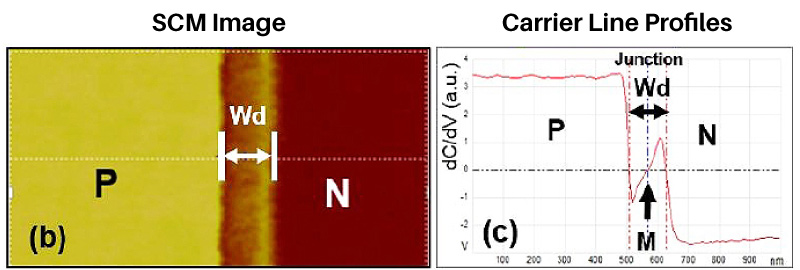

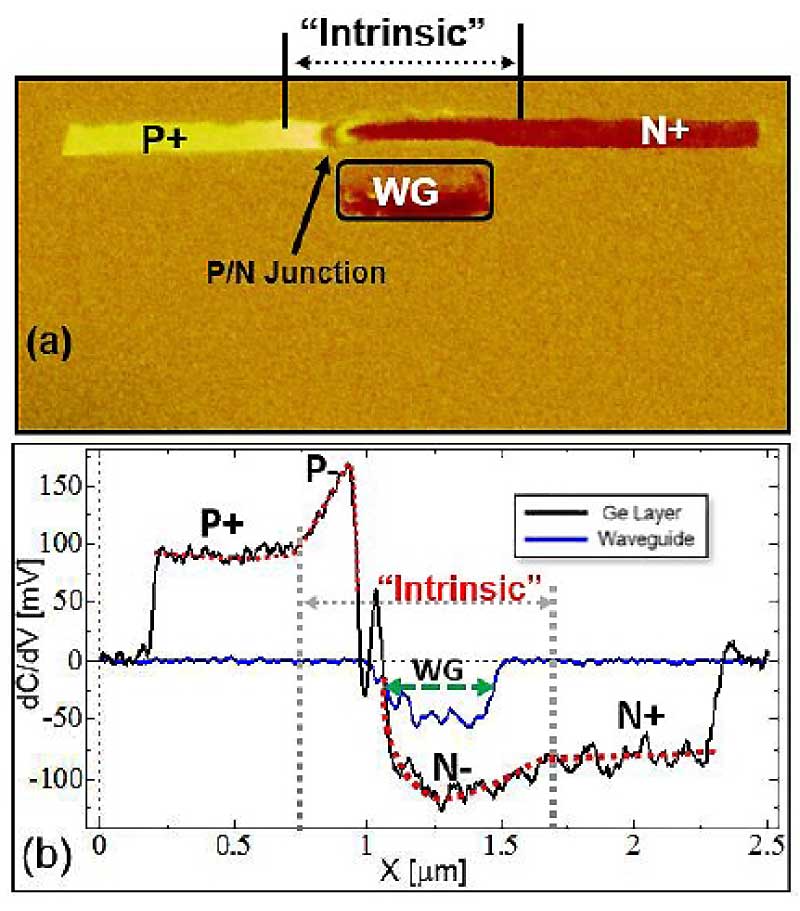

硅光子组件主要工艺是CMOS,藉由扫描电容显微镜(SCM)的分析技术可以量测PIN在不同工艺条件下,观察在本质层中空乏区宽度(Wd)的变化,图六说明经由SCM二维载子分布图(Mapping)影像以及从一维载子线分布(Line Profile),分别能区分P/N接面(Junction)的位置与Wd的示意图。

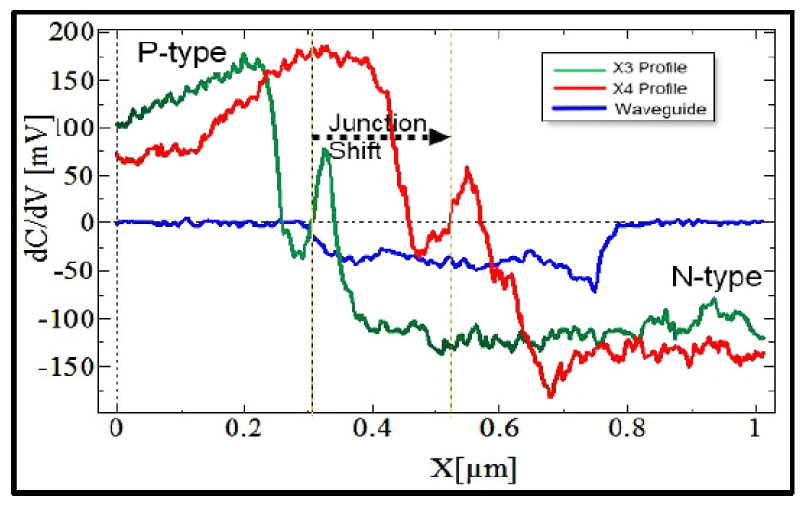

在图三中X3与X4两位置区域的剖面SCM一维载子分布的结果于图八中,可以量得p/n接面位置偏移了约215nm(两条虚线间距)。上述都是透过SCM,可观测出空乏区宽度(Wd)的变化,而空乏区的宽度决定电流流过的多寡,将会直接影响到组件质量与性能。

本文中谈到离子植入产生的晶格缺陷或是硅波导朝向本质层扩散现象,以及N/P dopant扩散速率的差异影响Wd宽度等,这些要素皆决定了硅光子组件的质量,都是目前研发单芯片硅光子工艺技术,所需面对的课题。

此外,在设计Waveguide材料或形状,以及其他相关工艺的研发中,均可藉由奈米材料分析技术如TEM、EDS与SCM等,宜特科技拥有大量材料分析实战经验,可以提供客户有效的浓度分布的数据分析,并以此依据改善研发工艺细节。

事实上,现有相关硅光子产品大多是将数字交换芯片与光收发模块(Transceiver)利用先进封装包装在一起,称为共同封装光学(CPO, Co-Packaged Optics)的方式商品化,这种产品仍有耗能与体积大的问题,未来采用「硅光子单芯片」能真正达到短小节能的目标,该技术可以提供高速、节能的整合解决方案,从而彻底改变数据中心、人工智能、电信、感测和成像以及生物医学应用等行业。

宜特材料分析实验室长期观察半导体产业趋势,我们认为尽管硅光子技术存在整合和设备制造相关的挑战,相信各家大厂仍会持续加速研发脚步,在全球共同努力下,突破摩尔定律关键技术的诞生终将指日可待。本文与长久以来支持宜特的您分享。若您有相关需求,或是对相关知识想要更进一步了解细节,欢迎洽询 +886-3-579-9909 分机 6613 张先生 / Email: sa_tw@istgroup.com ;

marketing_tw@istgroup.com。

參考文獻:

[1] Daniel Benedikovic*, Léopold Virot, Guy Aubin, Jean-Michel Hartmann, Farah Amar, Xavier Le Roux, Carlos Alonso-Ramos, Éric Cassan, Delphine Marris-Morini, Jean-Marc Fédéli, Frédéric Boeuf, Bertrand Szelag and Laurent Vivien, “Silicon–germanium receivers for short-wave-infrared optoelectronics and communications”, Nano-photonics 2021; 10(3): 1059–1079

[2] -[8] J. Nxumalo, Y. Wang, M. Iwatake, C. Molella, A. Katnani, J. Orcutt, J. Ayala, K. Nummy, “Characterizing junction profiles in Ge photodetectors using scanning capacitance microscopy (SCM) and electron holography”, 978-1-5386-4513-0/18 ©2018 IEEE