发布日期:2026/03/25 破坏性失效分析DPA

发布单位:iST宜特

芯片在厂内经过数千小时可靠性验证且电性测试数据完美Pass,原以为稳拿订单,没想到送交 Tier 1厂后,却在进料检验(IQC)被揪出「焊点裂纹」惨遭整批退货。这不仅让研发心血付诸流水,更直接威胁到刚拿下的Design Win。到底如何做才能确保产品真正零缺陷呢?

破坏性失效分析DPA

破坏性失效分析DPA

进入2026年,随着「软件定义汽车(Software-Defined Vehicle, 简称SDV)」与「区域架构」(Zonal Architecture)成为产业主流,在SDV趋势下,芯片需具备极高的效能余裕以支持未来的软件升级;而区域架构则让大部分的芯片必须安装在更靠近马达等热源与震动源位置,而在高压、高热、高震动的极端环境下运作。

近期AEC车电协会(Automotive Electronics Council)频繁针对先进封装修正测试标准,正是体认到ATE(Automatic Test Equipment)电性数据已无法全面涵盖结构疲劳的风险。包含 Tesla、NVIDIA与高通(Qualcomm)等大厂,在将高性能运算(HPC)芯片导入车载系统时,已将「Zero Defect」的要求从芯片的「功能正常」提升至「结构绝对完整」。若您的产品潜伏结构隐患,即使侥幸通过 ATE 测试,也难逃时间的审判。

事实上,ATE Pass 仅代表「功能」合格,而 DPA(破坏性物理分析)才是验证「寿命与结构」的关键。若不想让即将到手的量产门票毁于一旦,在研发阶段就导入DPA进行深度的物理诊断,是迈向车规级零缺陷的必经之路。因此,本篇《宜特小学堂》将透过DPA(Destructive Physical Analysis,破坏性物理分析)剖析三大案例,助您的车用产品安全上路。

一、什么是 DPA?为什么它是车规的「照妖镜」?

简单来说,DPA 就像是「身体健康检查」。有别于一般 FA(故障分析)是在坏掉后才找原因,DPA是在产品判定「电性功能 Pass」的状态下,随机抽样进行一系列的破坏性拆解与检测。

它的目的只有一个:检查那些「躲过ATE测试」的潜在性内伤。

例如:打线接合面其實已出现裂痕,但剩下的接触面在ATE电性测试下导通依然良好,显示Pass。这种芯片一旦上车,经历几次热胀冷缩就会彻底断裂。这种「未爆弹」,只有透过DPA把它切开来看,才能无所遁形。

二、别再说客户没要求!AEC早就写得清清楚楚

很多IC设计工程师会问:「AEC-Q100我都跑完了,客户也没特别说要做 DPA,我有必要多花这笔钱吗?」

根据 AEC 规范,DPA 绝非选配,而是确保结构质量的必要手段。除了针对分离式组件的 AEC-Q101、光电半导体的 AEC-Q102 及板阶可靠性的 AEC-Q007 皆将 DPA 列为必测项目外;针对铜线(Cu Wire)制程的 AEC-Q006,更制定了最严格且具体的破坏性分析标准,成为所有采用铜线封装的车用芯片必须跨越的硬性门坎。

如果你为了降低成本,而将封装从「金线」转为「铜线(Cu Wire)」,那么你已经自动落入AEC-Q006的规范范畴。由于铜线较硬,容易在制程中造成底层铝垫(Al Pad)破裂(Cratering),因此 AEC-Q006 明确要求必须进行DPA相关项目的验证。

如果你不想被Tier 1稽核时抓包,以下这些是AEC-Q006里提到必须关注的 DPA 重点项目:

1. Wire Bond Shear (焊球推力测试):透过横向推力确认铜球与铝垫的结合质量。检视金属间化合物(IMC)的生成状况,了解打线底层接口是否有剥离或裂痕。对于Cpk (Process Capability Index) 数值分布有严格要求,以证明制程能力稳定。

2. Wire Bond Pull (焊线拉力测试):透过垂直拉力着重测试打线颈部和第二焊点是否牢固。透过分析拉线后的失效模式(Wire pull failure modes)来了解断裂发生的位置,与Wire Bond Shear一样会确认Cpk数值是否于规范内。

3. Crater Test (弹坑测试): 这是铜线制程的关键检查。移除焊垫金属层,检查下方是否有因打线应力造成肉眼看不见的「隐形裂纹(Cratering)」。

4. Cross-Section (切片分析):使用 SEM(电子显微镜)检查整个样品的完整性,包含芯片、模封胶(Molding compound)、黏晶胶(Die attach)、导线架(Lead frame)之间的接口状况,以及打线第一和第二焊点下方有无微裂纹与脱层异常。

5. 内部目检 (Internal Visual):检查封装体内芯片表面,是否有保护层裂纹或芯片缺角等损伤。

三、宜特案例分享:解决工程师最头痛的隐性失效

以下是宜特协助 IC Design House 在量产前,透过 DPA 拦截的三大灾难现场:

(一)案例一:护层裂纹拦截术—破解ATE的侦测延迟假象

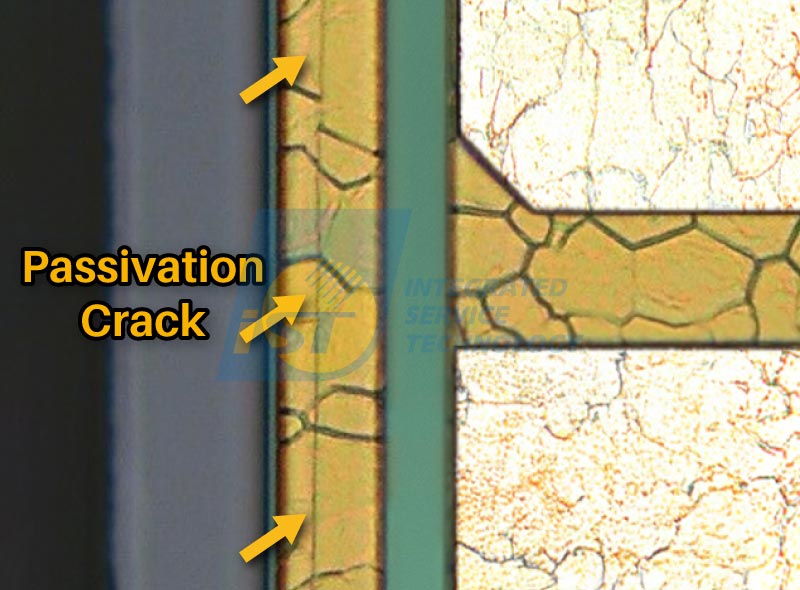

某车用 IC 客户在进行可靠性测试后,ATE 显示全数通过。但宜特工程团队透过 DPA 的 Phase 1 破坏性分析发现,部分样品的 Passivation(护层)已出现微小裂纹。进一步透过横截面观察,确认裂纹已延伸至金属层边缘。

这说明了仅有电性测试却无 DPA 拦截的状态下,这批货一旦装上车,数个月后可能将引发大规模客诉甚至灾难性的性命伤害疑虑。

图一:DPA 显示护层裂纹,暴露ATE测试中看不见的可靠性风险。

(图片来源: iST宜特科技)(二)案例二:铜线打线(Cu Wire)界面诊断—直击 AEC-Q006 最在意的焊点疲劳

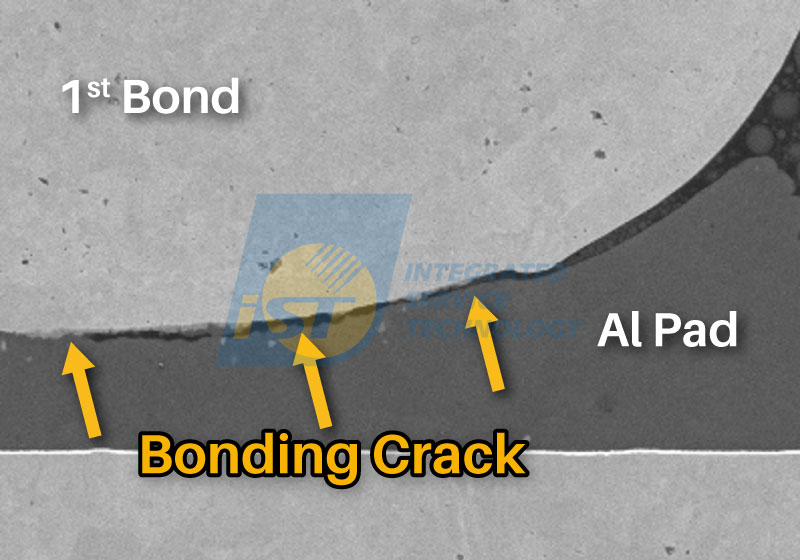

为了兼顾成本与效能,许多车用芯片将制程转向铜线(Cu Wire)封装,但这也带来了更严苛的可靠性挑战,尤其是 AEC-Q006 规范中最在意的高温应力与金属疲劳。在铜线封装制程中,焊点与铝垫间的 IMC覆盖率是讯号传递可靠性的指针。

某客户希望优化打线参数,虽然初步电性测试无异,但宜特透过 DPA 的分析与测试手法,发现特定参数下的 IMC 生长不均,且推力值虽在规格内但故障模式出现了「Bonding crack」征兆。这正是典型的「当下 Pass、长期 Fail」假象。

图二:DPA 显示焊点缺陷,暴露ATE测试中看不见的可靠性风险。

(图片来源: iST宜特科技)(三)案例三:界面分层深度定位,解决热膨胀系数不匹配的灾难

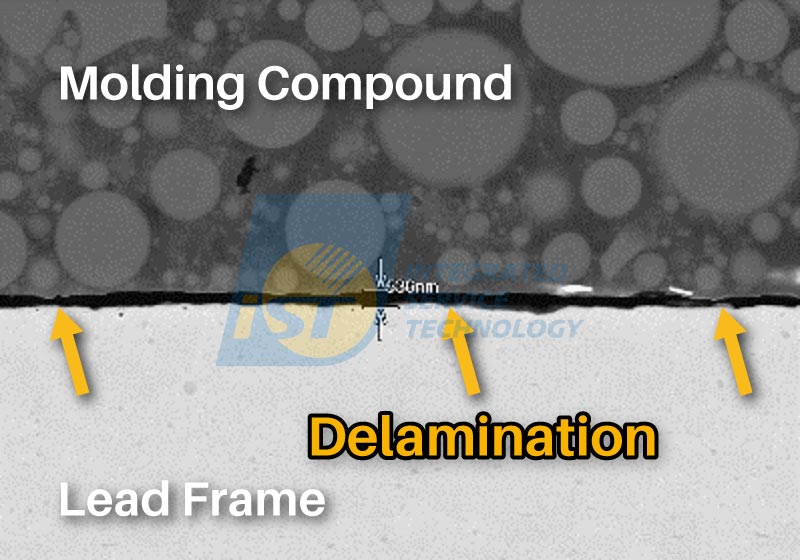

在车规可靠性测试后,宜特运用 DPA手法,整合非破坏与破坏性分析技术,针对封装结构进行全面性的「身体检查」。此分析结果不仅精准定位出导线架与模封胶间的界面分层位置,更进一步溯源发现,分层主因系导线架与模封胶这两类异质界面间的热膨胀系数(CTE)不匹配。

这项关键发现不仅厘清了Failure原因,更提供客户具体的改善方向,协助客户重新筛选胶材,从根本提升了整体结构的热机稳定性。

图三: 透过DPA深度切片与扫描技术来检查封装结构的完整性

(图片来源: iST宜特科技)

以电性结果通过AEC认证只是入场券,然而迈向「零缺陷」的核心课题,在于如何补齐电性测试看不见的盲点。对于IC设计公司而言,DPA 不应该被视为一项「多余的成本」,而是一份「确保出货安全的保险」。

当你的竞争对手只拿得出ATE报告,而你能同时附上第三方公正实验室的 DPA完整分析报告,这代表的不仅是质量,更是你对车规理解的专业度。别让一颗1美元的芯片,毁了你千万美元的订单。在送样给Tier 1之前,先透过DPA做最后一次的健康检查吧。

中国免费咨询电话 400-928-9287 | Email: marketing_chn@istgroup.com;marketing_tw@istgroup.com