发布日期:2026/04/14 硅光子CPO失效分析

发布单位:iST宜特

硅光子芯片一旦经过封装后便难以进行重工工艺,您该如何确保昂贵的ASIC芯片不会因为一颗微小的PIC光学组件失效而整颗报废?本文将拆解硅光子PIC五大部件最具代表性的失效模式,突破量产「盲对准」的最后一哩路。

硅光子CPO失效分析

硅光子CPO失效分析

NVIDIA黄仁勋预期 2027 年 AI 基础设施将达兆元规模,但传输瓶颈导致 GPU 使用率低于 20%。为突破限制,NVIDIA 与台积电积极布局 CPO(共同封装光学),透过 COUPE 技术实现光电 3D 异质整合,预计 2026 年迈入量产元年。

然而,从「电」转「光」是全新的战场。工程师面临的不只是漏电,更是漏光、光耦合偏差与讯号衰减等棘手失效。当设计走向实体产品,最关键的挑战,便是如何透过严谨的验证,确保这项高价值技术的可靠性与寿命。

之前我们已从硅光子组件组成与决定效能的关键(阅读更多:「光」革新突破半导体极限 硅光子芯片即将上阵),进而分享对应的解决方案(阅读更多:硅光子开发为何这么难?验证手法是关键),以及如何突破硅光子量产的核心难关(阅读更多:硅光子CPO量产见曙光!从「漏电」到「漏光」如何迎刃而解?)。

本文将继续带领IC工程师转换视角,从看诊电性芯片的「神经内科医生」变身为治疗硅光子疾病的「眼科医生」。我们将针对光子集成电路(PIC)的五大关键部件,详细剖析其操作原理、常见失效模式以及尖端的失效分析(Failure Analysis, FA)技术,协助产业界打通硅光子量产的任督二脉。

一、CPO三大核心架构:从「离散外挂」走向「异质整合」

CPO的核心概念,是将原本独立的光收发模块与高阶交换器芯片(或运算芯片)整合在同一个封装载板上,大幅缩短电讯号传输距离,进而降低功耗与延迟。

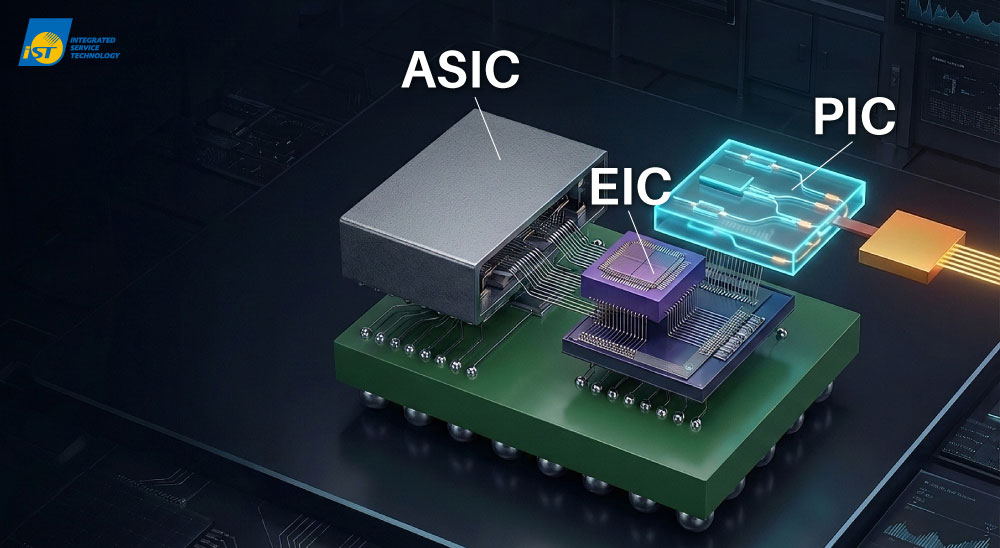

在CPO架构中,主要包含三大核心单元:由负责运算的系统大脑ASIC、扮演电讯号桥梁的 EIC,以及执行光电转换与传递的PIC 三大核心单元组成。运作时,ASIC 处理后的电讯号经由 EIC 驱动与放大,最后交由 PIC 转化为「光」进行高速传输;这种紧密整合虽带来效能飞跃,却也面临了「光电整合」的质量挑战。

图一:CPO三大核心架构—ASIC、EIC和PIC。

(图片来源: iST宜特-AI辅助生成制作)二、PIC五大关键部件与失效模式

相较于业界已熟稔的 ASIC 与 EIC 失效模式,PIC (光子集成电路) 才是 CPO 验证中最陌生的战场。 PIC 内部五大关键部件各有独特的物理机制,也衍生出截然不同的失效路径;要精准定位并排除这些微观病灶,极为仰赖尖端的失效分析(FA)技术,才能在量产前完成最后的风险收敛。

图二:PIC芯片五大关键部件示意图,每个部件都有独特的物理机制与失效模式

(图片来源: iST宜特科技)(一)光栅耦合器 (Grating Couplers, GC) :

- 操作原理:

利用沟槽结构让外部光纤以特定角度耦合进入芯片波导。需精准计算角度与尺寸,直接影响收光效率与偏振选择性。 - 常见失效模式:

对准偏差、工艺残留物或环境掉落尘粒导致表面型态变异,或应力造成的物理损坏,皆会引发漏光或波长偏移。 - 分析技术:

宜特实验室可透过扫描式电子显微镜(SEM)、能量色散X射线光谱仪(EDX)、聚焦离子束(FIB)与穿透式电子显微镜(TEM),进行微观缺陷分析,并透过切片检查确认雷射与光栅耦合的实体完整性。

(二)光波导 (Waveguides, WG) :

- 操作原理:

负责光传输的通道。利用核心与包覆材料的折射率差形成「全反射」,将光束限制在通道内。硅、氮化硅或碳化硅均为常用材料。 - 常见失效模式:

需严格检视材料吸收率,过高将导致传输衰减;波导侧壁粗糙会引发散射损耗;此外,热稳定性对折射率的影响亦至关重要。 - 分析技术:

宜特透过精细的切片分析(Cross-section),以观察波导传输信道的结构尺寸是否合乎设计,并检视是否有导致光讯号散失的结构变异或缺陷。

(三)热调谐器 (Heaters) :

- 操作原理:

藉由电流产生热能改变波导局部温度,引发折射率改变以微调相位。常用材质包括钛 (Ti)、钨 (W) 或氮化钛 (TiN)。。 - 常见失效模式:

导线间距过近或绝缘不良易导致漏电,甚至遭受 ESD 静电击穿造成结构烧毁,或因热隔离 (Thermal Isolation) 不佳干扰邻近组件。 - 分析技术:

宜特针对漏电点进行横截面检查,并配合精密层次去除 (Delayer) 分析,逐层寻找烧毁或漏电的确切位置。

(四)PN接面调变器 (PN Junction Modulator) :

- 操作原理:

对 PN 接面施加逆向偏压以改变空乏区大小,进而调整折射率与光速。透过干涉原理,将「电讯号 (0 与 1)」转化为「光讯号」。 - 常见失效模式:

高温引发的瞬时失效 (热飘移)、ESD 永久性击穿,以及离子植入浓度变异导致调变效率低下。 - 分析技术:

透过扫描电容显微镜(SCM)或原子力显微镜(AFM),将载子浓度与掺杂轮廓具象化,以确认是否符合原始设计。当然,PN接面的切片检查也是不可或缺的一环。

(五)锗光电侦测器 (Ge Photodiodes, PD) :

- 操作原理:

负责将光讯号重新转回电讯号。业界常于硅工艺中加入锗 (Ge) 元素,以大幅提升对特定波长光讯号的感测灵敏度。 - 常见失效模式:

最大的致命伤是暗电流(Dark Current)过高。这通常源于磊晶生长的晶格缺陷,残留金(Au)、铝(Al)等金属微污染,皆可能形成漏电路径。其他亦可因受外在热应力破坏或因长期硬件操作不当或突发大电流导致组件失效或实体烧毁。 - 分析技术:

锗光电侦测器的分析极具挑战性。宜特科技透过电子束诱发电流(EBIC)技术进行高分辨率的电性失效定位,再辅以穿透式电子显微镜(TEM)、能量色散X射线光谱仪(EDX)以及二次离子质谱仪(SIMS)进行深度的晶格缺陷与金属污染分析,确保找出导致锗光电侦测器失效的真凶。

- 操作原理:

三、测试与量产的终极难关:盲对准与KGD的数学陷阱

在推进硅光子量产时,工程师会遭遇有别于传统IC制造的挑战,这不仅是物理极限的对抗,更是一场关于成本与良率的数学陷阱。

(一)光耦合的「盲操作」:

要把光顺利打进比头发还细的波导,对准误差必须控制在0.5微米以内。传统测试需反复调焦与换角,极低的产出率(Throughput)与高昂时间成本,直接拖累产品上市时程。

(二)KGD(Known Good Die)的良率乘法陷阱:

在异质整合架构下,,总良率是各组件的「乘积」。若在封装后才发现 PIC 失效,损失的不只是廉价组件,更是与其封装在一起、价值数千美金的高阶 ASIC。这种「小零件拖垮大芯片」的风险,是让毛利归零的致命伤。

(三)传统推测法的极限:

过去的光学晶圆测试(OWAT)多依赖反射量测,仅能得知「总体插入损耗」。工程师无法在封装前判定确切光损数值与病灶,导致风险一路被带入最终产线。

四、 验证标准与突破:从「推测」到「可视化」精准量测

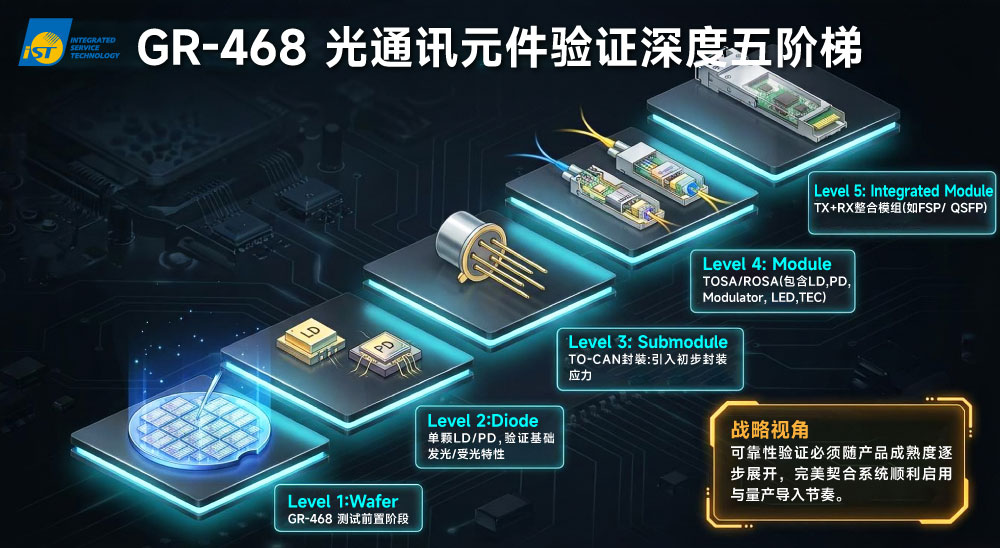

为破解测试盲点,业界建立起「定性」与「定量」的双轨防线,并参考电信级 Telcordia GR-468 标准,执行从晶圆(Level 1)到整合模块(Level 5)的五阶验证。

这套规范不仅包含物理应力的 Pass/Fail 定性测试,更强调 in-situ(原位)动态监测。透过长期监控雷射电流、波长飘移与光电侦测效率等关键参数,工程师能精准捕捉导致系统崩溃的微小病灶,实现验证过程的全面可视化。

图三:GR-468规范示意图,从晶圆到最终整合模块的完整生命周期,可分为五个验证阶梯

(图片来源: iST宜特-AI辅助生成制作)

硅光子与 CPO 是突破 AI 算力瓶颈的关键,但复杂的失效分析路径与良率陷阱,唯有透过精准的「定性与定量」分析才能化解。若您有相关需求。立即回信与我们联系,让我们一起突破硅光子的研发瓶颈!

中国免费咨询电话 400-928-9287 | email: marketing_chn@istgroup.com; marketing_tw@istgroup.com