发布日期:2025/12/15 硅光子 CPO

发布单位:iST宜特

全球AI大厂倾注资源,顶尖工程师绞尽脑汁。为什么硅光子迄今仍无法顺利量产?从电路跨入光路,隔行如隔山。硅光子这场史诗级战役,最终谁能戴上胜利桂冠?

硅光子 CPO

硅光子 CPO

2025年,AI高速运算的战火持续升温。全球AI供应链都面临同一件事:

电子带宽已逼近物理极限,光电融合已不再是可选项,而是必然趋势。而在这波升级浪潮中,最受瞩目的关键,就是硅光子(Silicon Photonics)技术与 CPO(Co-Packaged Optics)封装。

从 NVIDIA 宣布导入硅光子技术、Broadcom 加速以太网络新品布局,到台积电全力推进 COUPE 光子引擎,这场「光速竞赛」已经全面开跑。不只产业巨头动起来,台湾也将硅光子列入「AI 新十大建设」之一,预计在2028年达成硅光子供应链自主。经济部更投入 29 亿元光电前瞻技术计划,要让高雄成为未来的硅光子核心基地。

但即便拥有全球顶尖的工程团队与政府资源,要让硅光子走向量产,仍面临许多难关。因为当光路(Photonic Integrated Circuit,简称PIC)被整合进芯片,整套验证流程从电路(Electrical Integrated Circuit,简称EIC)问题瞬间跨到 PIC光子问题。这让许多研发团队,即使突破架构设计,最后仍卡关在硅光子测量速度太慢,验证时程跟不上设计周期;光损位置抓不准,确切数值无法取得;封装后出现不可逆故障、良率难提升等挑战。

之前我们已针对硅光子五大研发挑战,分享对应的解决方案(阅读更多:硅光子开发为何这么难?验证手法是关键)。本篇宜特小学堂,将带你进一步拆解硅光子量产的核心难关,并分享我们如何协助工程师加速 CPO 研发,进而成功迈向量产。

一、硅光子为何成为 CPO 的核心技术?

硅光子组件,包含波导(Waveguide)、调制器(Modulator)、分波器(Demultiplexer/Mux)、耦合器(Coupler)以及多数的光电二极管(Photodiode,PD)皆能直接采用与半导体芯片相同的CMOS(互补式金属氧化物半导体)工艺制造(阅读更多:「光」革新突破半导体极限 硅光子芯片即将上阵)。

这意味着光子器件可沿用既有的晶圆产线大规模量产,并具备与电子电路(EIC)同封装或同晶圆整合的能力。

当光(PIC)与电(EIC)集成于同一平台,便能打破电子互连的物理极限,实现:宽带、低功耗、高速传输、高抗干扰能力,并有效避免电子互连中常见的 Skin effect(趋肤效应)、Crosstalk(串音)与IL(Insertion Loss,插入损耗)急遽上升等问题,使SerDes互连能耗可从 15–25 pJ/bit 降至 1–3 pJ/bit,同时大幅降低热管理负担。

二、技术再美好,落地却不易:硅光子量产前的三大验证挑战

虽然硅光子具备高速与低功耗优势,但对于原本习惯处理电子电路的工程师来说,隔行如隔山,PIC 代表的是全新的物理现象与测试方法。宜特观察,目前产业在推动硅光子量产时,验证阶段普遍面临三大关键挑战:

(一)硅光子组件测试速度缓慢,严重拖累开发时程

首先,最令人苦恼的是,目前硅光子组件的测试速度,和电测相比有巨大的落差,远远跟不上当前高速接口与AI芯片的开发节奏。

在测量IL、PDL(Polarization Dependent Loss,偏振依赖损耗)、Responsivity(光响应度)和Spectral Response(频谱响应)时,都需逐波长扫描取样。另外,与电路可快速直接用探针Probe测试完全不同,硅光子组件无论在光纤耦合、波导测试,或是调制器测量时,每测试一颗都要重新调焦、调整入光角度。种种因素导致目前硅光子组件测试速度相当缓慢。

(二)电路问题可以测量,光损问题却常常只能「推测」?

目前业界的硅光子光学晶圆验收测试(Optical Wafer Acceptance Test,简称OWAT),大多仍依赖光反射测量(Reflectometry)与频谱分析(Spectral Analysis),去推断可能漏光位置。但这种方法只能「推断」,并非「精准」掌握。

多数晶圆厂只能进行总体插入损耗(Total IL)检查,工程师能看到光效能变差,却难以判断光损的确切数值与来源。当缺乏确切位置与量化数值时,将导致设计、封装与量产端就容易在同一问题上反复卡关踩雷,难以有效收敛。

更困难的是,PIC的光讯号比电子讯号更敏感,而造成光损的因素也更分散且复杂,使光损不仅难以预测,更难以靠传统光学测量方法进行来源定位。

由于需要硅光子技术的多数应用,都是高速接口与AI运算相关的驱动与控制电路,因此所搭配的EIC往往采用5nm、3nm等先进工艺,单颗芯片成本相当高昂。相较之下,PIC多以成熟工艺生产,成本明显较低。若等到异质整合阶段(如PIC与EIC贴合、组成CPO模块)才验出PIC的光损问题,将连带造成整颗EIC无法回收,整组模块也只能报废,损失将成倍放大。因此,PIC必须在晶圆阶段就完成精准筛选。

因为风险极高,PIC芯片常被迫全检(100% inspection),以避免在PIC与EIC贴合后才发现问题。然而全检不仅耗时、成本极高,也无法从根本上改善硅光子量产阶段的设计迭代效率。这些测量上的限制,正是硅光子从技术突破迈向大规模量产时所面临的最典型、也最难缠的瓶颈之一。

(三)封装后才发现隐藏热源,造成低良率风险

由于硅光子组件高度整合、光与电距离极近,模块内部往往潜藏局部热源。更棘手的是,这些微量热源往往肉眼不可见,也无法透过传统电测侦测。工程师通常只能从IL、PD Responsivity或BER变差等「结果」观察到问题,但却无法直接判断热源位置、强度与根本原因。

若未在wafer或芯片阶段提前检出,实时监测与定位,后续在封装与上机运作后,便可能引发波导漂移、光损增加、热光效应失衡、甚至组件提早老化等失效模式。整颗模块可能无法返修,只能报废,造成CPO与光模块的良率大幅降低。

三、宜特 × 光焱科技:硅光子验证痛点的完整解方

为协助产业突破这些瓶颈,宜特与光芯片测量设备商-光焱科技(Enlitech)结盟,整合「宜特懂电、光焱懂光」的双强实力,共同打造出一个从硅光子组件、晶圆到模块的光电整合测量平台。能帮助研发工程师,在开发阶段就快速掌握光衰与缺陷位置,大幅缩短研发周期,加速硅光子技术迈向量产化。

(一)从「推测」正式进入「证据测量」时代:不只精准看出光损位置,连确切数值都能提供

宜特导入光焱科技的Night Jar™ 硅光子测试解决方案 (Silicon Photonics Testing Solution),搭配全球独家专利技术,可针对晶圆、芯片与模块进行高速光损(Insertion Loss)Mapping。

过去OWAT (Optical Wafer Acceptance Testing) 只能告诉工程师「光进光出总光损多少」,Night Jar™ 则能告诉工程师哪个die、哪个结构异常、漏光位置在哪里?漏光和光损精确数值是多少?

且Night Jar™ 测量流程如同操作OM 或X-ray一样直觉,与目前业界光学设备相比,Night Jar™ 拥有更清晰的漏光影像、可视化光损分布、每个光子组件的定量光损值(Quantitative IL Value),亦可做到局部光损定位。

这是传统OWAT或一般光损仪器完全做不到的能力。

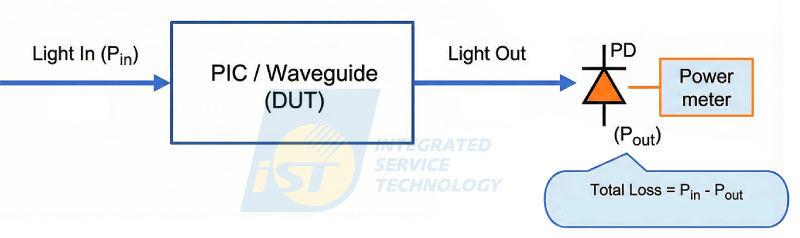

图一:传统OWAT光学测量示意图。此法只能告诉工程师「总光损多少」,却无法得知漏光位置和光损的精确数值。

(图片来源:宜特科技)

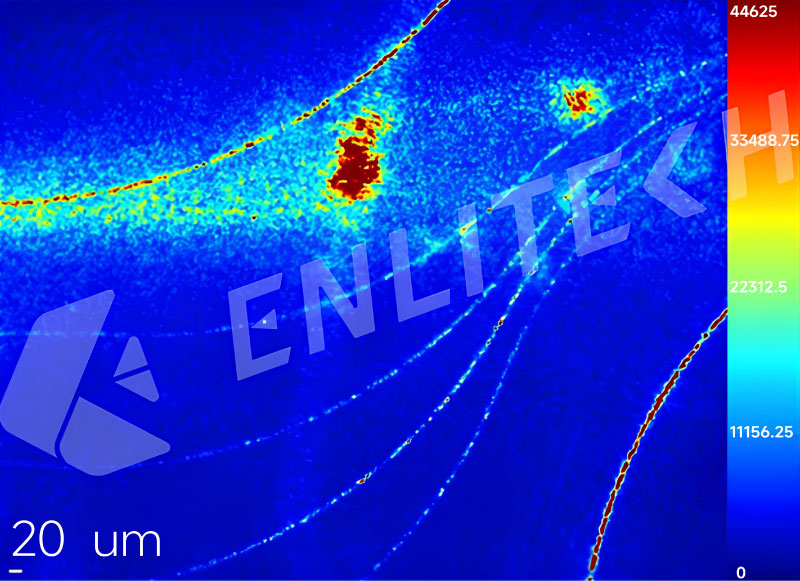

图二:Night Jar™ 可让使用者直接「看到」光损的位置与损失量,能够「看到」光是从哪里、哪个结构中溢出或损耗的。这对于故障分析和设计除错非常重要。

(图片来源:光焱科技)(二)速度与精度双突破,终于可跟上研发需求

Night Jar™最大特色是速度极快,每秒即可完成一个区域的影像拍摄,整体效率比市面上快上一倍之多。而平台内建的高精度耦光对位模块(Alignment Module)精准度可达 0.2 nm,显著提升测量的稳定性与重复性(Repeatability),使光损数据更可靠、更具工程分析价值。

图三:光焱Night Jar™对于市面上硅光模块的实测能力。

(图片来源:光焱科技)(三)从光损分布到热源影像,同步掌握模块隐藏风险

透过Night Jar™的光损Mapping,我们能在研发早期精准标记异常光衰的区域。若进一步结合光热影像(Optical-Thermal Imaging)分析,可同步揭露模块中的潜藏热源(Hotspots),协助工程师在封装前就掌握:热漂移(Thermal Drift)、波导附近的局部过热、调制器或雷射源的热累积、光电二极管(PD)受热造成的性能变动等,这是传统电测或封装后验证难以覆盖的。

(四)精准光损定位后,进入更深入的物性与结构分析

当光衰位置被正确锁定后,工程师便能将分析范围聚焦在特定组件及区域,后续即可进行:PFA(Physical Failure Analysis,物性分析)和MA(Material Analysis,材料/结构分析)。

透过 SEM、Dual-Beam FIB、Plasma FIB、TEM、X-ray、SIMS 等手法,能将隐藏在波导、耦合器、调制器等组件内部的微缺陷完整揭露,加速设计收敛与工艺优化。

(五)CPO模块可靠度测试:以 IL 变化为核心判断依据

在光学组件通过前段测量后,组装完成的CPO光电模块,如COUPE(Compact Universal Photonic Engine)等產品,可直接进入全项可靠度测试流程,包括:TCT(Temperature Cycling Test,温度循环)、HAST / 湿热测试、振动(Vibration)、落尘(Particle Contamination)等。所有测试均以IL变化量 作为通过与否的标准,确保模块能达到国际大厂规格。透过数据化与统计化测量,可有效量化风险,协助工程师做出更精准的设计与工艺判定。

少走弯路,才能快一步,从电路跨向光路。要真正克服 CPO 光电整合的难题,在可靠度过关的情况下实现量产,这场仗,全世界都在看。而帮助你加快硅光子研发脚步的关键,就在于一站式的验证手法。从Substrate和Socket 设计、光/电测试、可靠度验证、故障分析和结构分析,到封装挑战的解决,流程越顺畅,光速时代,就越快到来。

中国免费咨询电话 400-928-9287 | email: marketing_chn@istgroup.com; marketing_tw@istgroup.com