发布日期:2024/6/18 AI芯片可靠性挑战

发布单位:iST宜特

不想被大AI时代抛在后头?确保芯片质量与可靠性是关键。而AI芯片面临的三大挑战:超高功耗、超低电压、异质整合,你知道该怎么迎战吗? AI芯片可靠性挑战

AI芯片可靠性挑战

OpenAI与Google日前于最新发表会中,揭晓了旗舰模型「GPT-4o」与「Project Astra」。当用户与其对话时,不但可相互传输文字、图像和音频,甚至另一端的机器人还可以透过手机屏幕,描述出用户身处的环境,并从使用者的口吻中,判断出使用者的情绪,聊到开心之处甚至还会大笑和歌唱,沟通上完全就跟真人如出一辙。

AI人工智能技术是透过仿真人脑的类神经网络,经过深度学习,取得对象特征参数,产生仿真人脑的判断能力。这看似艰深的AI技术,早已走进大众的日常生活,从生成式内容、自动驾驶、智能家居到医疗保健,从金融到制造业,应用广泛且深具潜力。可以预见,AI技术将继续引领创新,成为推动产业发展的重要引擎。

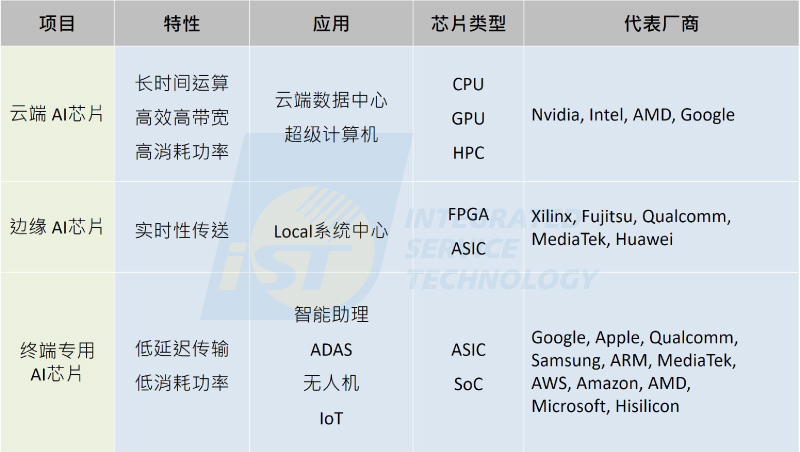

除了算法与大数据的演进与支持之外,硬件方面,AI芯片依不同的应用领域,不断往高效能、高带宽或低耗电等特性演进(表一)。然而这些特点,不仅会影响AI芯片的效能与寿命,甚至,也造成AI芯片可靠性试验设计手法、设备等,面临极大挑战。宜特可靠性验证实验室,为您归纳出AI芯片最常见的三大挑战与解决办法,本期宜特小学堂,将会逐一说明。

一、AI芯片最常见的三大挑战

(一) 云端AI芯片的超高功耗挑战:热消散与热平衡能力

数据中心的云端AI芯片,肩负人工智能的深度学习任务,必须提高效能运算,也因此将耗费大量电能,其单一颗芯片耗电量甚至超过200W(瓦),伴随产生的高热,将使得芯片老化速度加剧。

因此,一年必须连续工作365天的云端运算AI芯片,对老化产生的可靠性问题更需审慎评估。

可靠性测试原理必须抽样(sampling)一定数量的IC做实验,来预估整个母体的生命周期与故障机率。通常抽样的数量为77颗,当77颗数百瓦的芯片,一起在一台可靠性系统设备做1000小时的可靠性测试时,上万瓦的功率热能,将严格考验可靠性测试系统的热消散与热平衡能力。

唯有精准的热消散与热平衡能力,才能让每一颗芯片在执行各种不同运算模式时,芯片都能维持稳定的Junction温度(Tj)(PN接面温度),如此才能够准确预估IC的生命周期。因此,高效能云端AI芯片所产能的热能,该如何消散与控制,将是IC可靠性实验设计面临的一大挑战。

(二) 终端AI芯片的超低电压挑战:多组系统电源需求,挑战可靠性测试极限与硬件解决方案

终端AI芯片除了需要高运算效能之外,还必须具备低耗电特性,以满足其应用环境的需求。例如,行动装置、物联网 (IoT) 装置、无人机、电动车自驾辅助等,皆仰赖电池供电,因此低功耗设计至关重要。

随着半导体工艺不断进步,相同逻辑闸数下的动态电流越来越省电。然而,尺寸微缩的物理特性效应,却导致晶体管静态漏电流增加。摩尔定律指出,每两年晶体管面积可缩减一半,但这并无法让芯片的功耗密度减半,相同面积的芯片将会消耗比以往更大的电流。

为了降低功耗,除了采用低工作电压设计之外,多工作电压与多闸极电压的设计也十分常见。然而,对于可靠性测试系统而言,动辄10组以上的系统电源需求,将挑战可靠性设备电源数目的极限。

同时,1V或甚至低于1V的主电源(core power)低工作电压,将使得IC电源的余裕度(power margin)缩小,电路板上的电压降(power IR drop)或者电源涟波(power ripple),更容易造成IC可靠性测试出错。电压降不仅发生在主电源,因为主电源的降低,部分逻辑闸讯号源(Pattern)电压准位,也需要同步降低,这进一步造成硬件设计与测试上的困难,在在考验着可靠性测试系统能力与硬件设计。因此规划一个符合终端AI芯片需求的高温工作寿命(High Temperature Operating Life,简称HTOL)可靠性测试环境,从设备选择、PCB电路板仿真与制作,各种细节与设计上的考虑,皆必须较一般逻辑IC更为严谨。

(三) 异质整合挑战:热消散路径复杂化

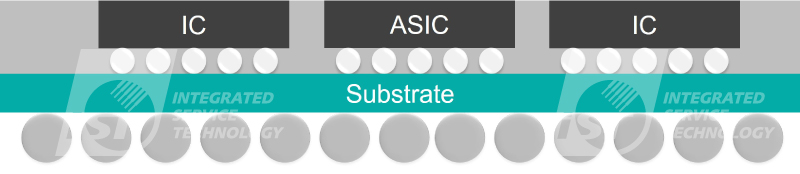

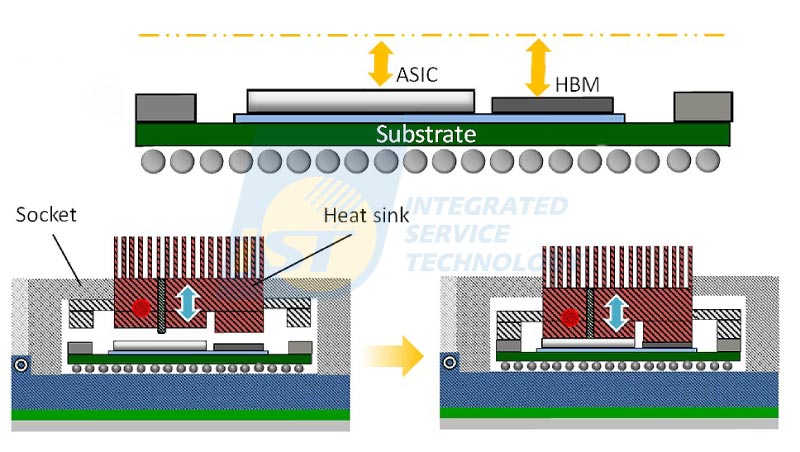

异质整合(heterogeneous integration)是AI芯片中的一项重要技术。为了加快不同芯片间的传输带宽,不同工艺的异质芯片被整合在一个封装内,常见的有高带宽内存(High Bandwidth Memory,简称HBM)、传感器(sensor)、微机电系统(Micro-Electro-Mechanical Systems,简称MEMS)和天线(antenna)等。经由硅通孔(Through-Silicon Via,简称TSV)、重分布层(Redistribution Layer,简称RDL)、凸块(bump)和中介层(interposer)等工艺手法,这些芯片可以并排或堆栈起来(如图一所示)。这将大幅度提升异质芯片间的数据传递效率,并降低耗电量。

但是,这种复杂的异质封装堆栈架构,热产生与热消散路径亦随之复杂,例如较大功耗芯片不一定位在封装中心位置,各个芯片厚度亦可能不尽相同,这将使得芯片产生的热消散与热感测方式不同于传统封装,如何在可靠性测试时正确量测与监控芯片温度变得更具挑战。

综上所述,如何面对热消散与热平衡能力、测试系统的电压极限,以及异质整合的热消散路径复杂化,是在进行可靠性设计验证时,必须克服的关键。对此,宜特可靠性验证实验室提出如下建议。

二、如何克服AI芯片的可靠性挑战

(一) 利用液态冷却系统,稳定控制高功耗AI芯片产生的热能

散热设计功率(Thermal Design Power,简称TDP),是CPU芯片对主板「散热能力」的要求规格。目前桌面计算机CPU的TDP规格最高在150瓦(W)左右,电竞玩家为了维持CPU长时间高效高频工作,往往升级主板、散热片、风扇等等配件,使得升级后的系统散热能力高于TDP要求,让CPU能长时间高频工作,而不会发生过热降频,甚至休眠等问题。

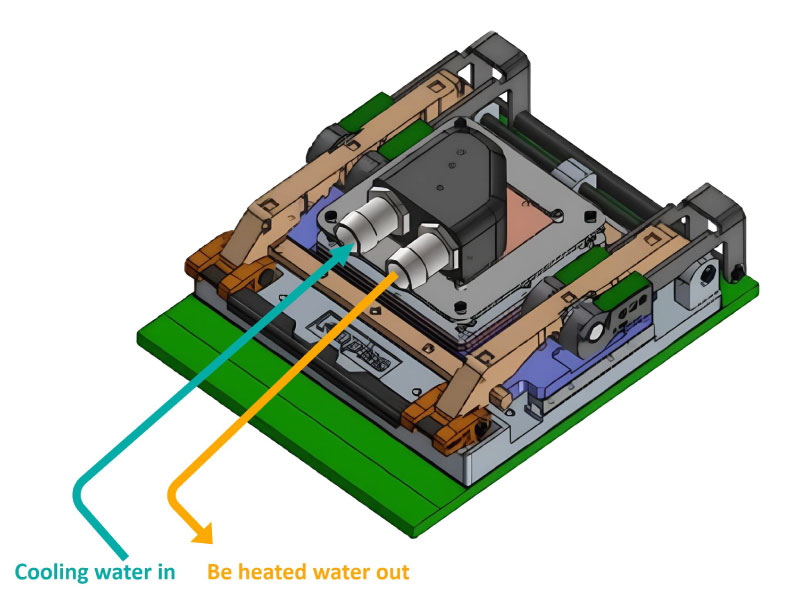

但是服务器及HPC等云端AI芯片,当前TDP规格已达200W以上超高发热功耗。而芯片因封装结构与材料等因素,已难以使用空气对流当散热媒介,将芯片junction温度控制在目标值。

尤其是在可靠性测试中,要求的目标温度高达125°C,这远远高于桌面计算机的70°C。通常在125°C时,芯片的功耗墙已经处于解锁状态,因此稍有不慎就可能导致芯片因高温而烧毁。因此,当对如此高功耗的IC进行高温可靠性测试时,测试系统必须具备更快速的散热能力。

宜特可靠性验证实验室的解法是,利用更高效的液态冷却控制调节系统(Liquid cooling system),搭配客制化液态循环socket(图二),此系统利用液态热交换速率优于气态的特性,以及实时监控芯片温度与调节液态流速等方法,稳定控制超高功耗AI芯片产生的热能,成功收集可靠性实验数据。

(二) 热二极管监控电路,监控IC本体温度

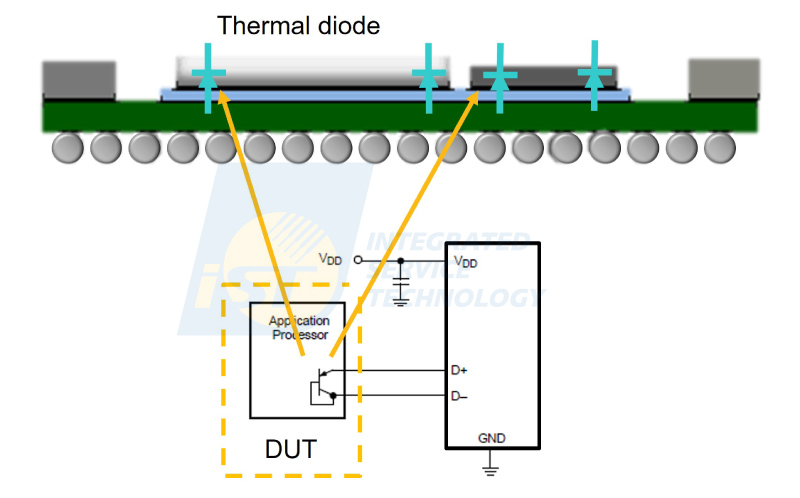

云端AI芯片的超高功耗,在进行可靠性测试时,容易因芯片本体温度波动太快,导致无法及时消散热能,造成产品非预期性故障,例如热失控(Thermal Runaway)。因此,当IC内建热二极管(thermal diode)组件时,宜特可靠性系统与可靠性测试板设计,可以客制化热二极管(thermal diode)监控电路,来监控IC 内部温度,将可监测到最实时与准确的接面(junction)温度(图三)。

此作法反应速度快,搭配前面提到的高效液态冷却控制调节系统,更适合超高功耗AI芯片快速温度变化,藉以提供实时热消散动作。此外热二极管(thermal diode)监控电路,可针对3D封装的多晶体(multi-chip)结构下,独立量测出各个芯片的温度,以达到更精确的可靠性数据收集。

(三) 客制化治具,贴合高低不同的裸晶(die)

AI异质整合芯片,里头的裸晶(die)高低不同,因此,在可靠性验证测试的治具准备,必须依照不同的芯片,客制化IC socket(测试座)和散热系统(heat sink)和热感测组件(sensor),才能够紧密贴合高低不同的裸晶(die),藉此增加热消散能力,温度量测与监控才能更准确(图四)。

(四) 测试电路板超前仿真,免去生产组装后效能不符

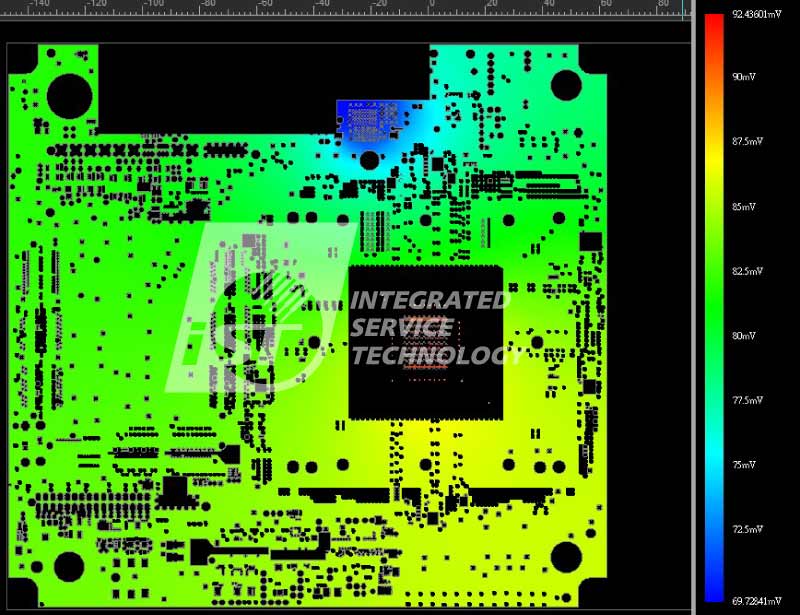

AI芯片采用先进工艺,超低的工作电压已来到1V以下。然而,当高电流经过电路板走线时,容易在电路板上产生由低到高的压降(DC IR drop)(图五),IR drop将压低原本已超低的工作电压,容易使得AI芯片因电源电压余裕度(Power voltage margin)不足而失效。

此外,当IC power抽载大电流时,也会产生各种频率的SSN(Simultaneous Switching Noise)。

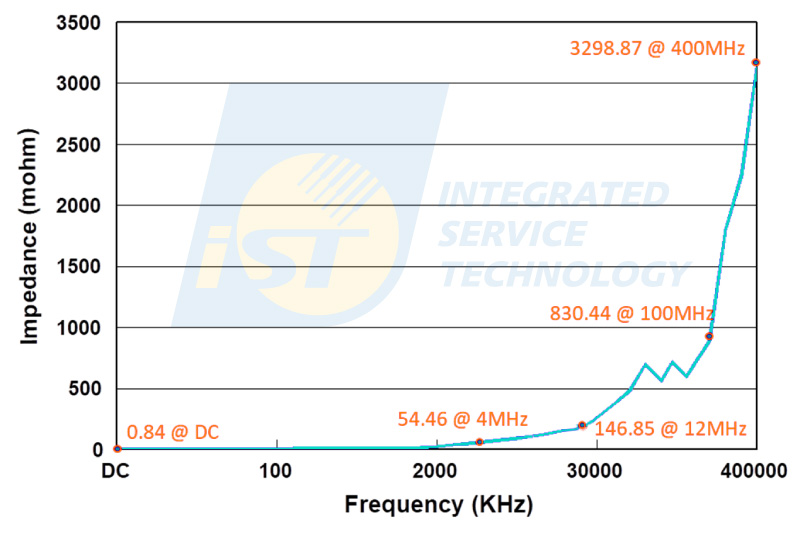

而电路板的电源层阻抗(Power plane impedance),在各种不同抽载频率下,因本身布线(layout)因素可能反映出高低不一的阻抗(impedance)值(图六),当阻抗值在某个频率下超越目标值时,就会造成严重噪声(Power AC noise)与涟波(Power ripple),也会使得AI芯片因电源噪声余裕度(Power noise margin)不足而失效。

另外,在传统的电路板设计中,由于在同一电路板上放置多颗芯片,每颗芯片的布线(layout)难以完全一致,导致芯片间测试电性存在差异,亦提高了设计与测试的困难度。

为了解决此问题,宜特可靠性实验室跳脱传统电路板设计思维,采用新的BI模块(Burn in module)设计理念,将电路板从原本的一板测试数颗芯片,微缩至仅测试单颗芯片。搭配目前许多布线(layout)辅助设计工具,即可在可靠性电路板设计初期,经由软件分析仿真,调整电源走线长短宽窄、灌孔点大小与数目、解偶合(decoupling)电容值与放置位置等,改善工作电压与讯号源IR drop与电源层阻抗等问题,避免测试电路板于生产组装完成后,才面临效能不符问题。此外,电路板设计微缩至单颗芯片,在测试老化实验时,能协助客户以个别待测物(Devices Under Test, 简称DUT)取得更多的实验参数,同时能针对各芯片的晶体管静态漏电流的不同,分别进行测试参数设定,进一步提升AI芯片的测试质量。

三、AI芯片可靠性解决方案速查表

宜特可靠性验证实验室从早期面对一般消费型芯片、车用芯片、5G芯片,到现今的AI芯片,已累积相当多的实战经验,可解决AI芯片可靠性试验设计时面临到的超高功率、超低电压,以及异质整合等问题,可以提供您精确的温度电压等可靠性测试数据,提升AI芯片的可靠性。

本文与各位长久以来支持宜特的您,分享验证经验,若您还有进一步的问题,请洽+886-3-579-9909分机6428徐先生 Email: web_cre @istgroup.com。