发布日期:2024/8/1 SRAM 失效分析

发布单位:iST宜特

SRAM 以其高速运作、低延迟和低耗能的特性,对于发展 AI 人工智能所需的高效运算及机器学习至关重要。当IC内部的SRAM出现问题,虽然已知异常位置,但碍于SRAM结构密集且重复性高,如何得知更多异常点信息,分析出异常真因是一大挑战。

SRAM 失效分析

内存分为两大类,第一类称为「非挥发性内存」(non-Volatile),比如Flash(闪存),用于长期储存数据;另一类则为「挥发性内存」(Volatile),包括DRAM(动态随机存取内存,Dynamic Random Access Memory)和SRAM(静态随机存取内存,Static Random Access Memory),可实时高速运算暂存数据。两者最大的差异,在于电源供应终止后,储存的数据是否会消失。

SRAM和DRAM属于挥发性内存,当芯片进行逻辑运算后,读写结果会暂存在SRAM和DRAM中,类似仓储的角色。只要电源供应不中断,SRAM和DRAM中的信息就会一直存在。一旦电源关闭,SRAM和DRAM内储存的数据将会消失。

相较于DRAM,SRAM具有静态存取特性,不需要周期性地刷新数据,因此更加节能,耗电量也更少。此外,SRAM透过开关晶体管即可读取数据,访问时间较DRAM快速,这使得SRAM成为应用于CPU和GPU中高速缓存的主流选择。

台积电在2022年IEDM (International Electron Devices Meeting )会议中表示,其三奈米(N3)工艺的 SRAM 面积仅比五奈米(N5)工艺缩小约5%,同时,Intel 4工艺的SRAM密度相较于Intel 7工艺也仅微缩了约23%。尽管大厂在不断精进的先进工艺中面临SRAM微缩挑战,SRAM技术在AI人工智能和高效能运算(HPC)芯片等先进应用中的重要性依然不减。

为满足高阶芯片在效能与功耗上的更高需求,芯片设计研发团队正不断寻求提升CPU性能的解决方案,SRAM芯片的堆栈设计便是其中之一。许多设计在CPU上方堆栈SRAM芯片,以达到 PPA(Power/功率、Performance/性能、Area/面积)的多重需求。但当IC中存在许多结构相同且密集的SRAM,一旦IC SRAM发生故障,如何进行故障分析,增强芯片的良率和稳定性非常重要。因此,本期宜特小学堂将从SRAM操作原理谈起,进而介绍常见的失效模式,再透过宜特故障分析实验室专业团队提供的分析协助您找出异常点真因。

SRAM 失效分析

SRAM 失效分析

一、SRAM的读写原理

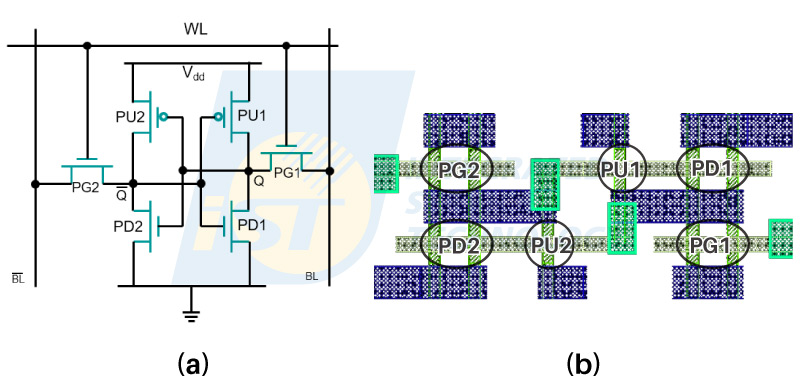

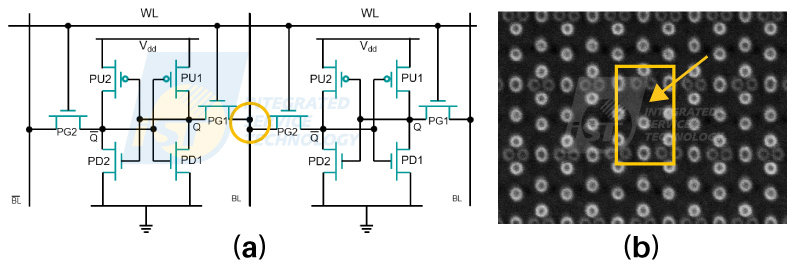

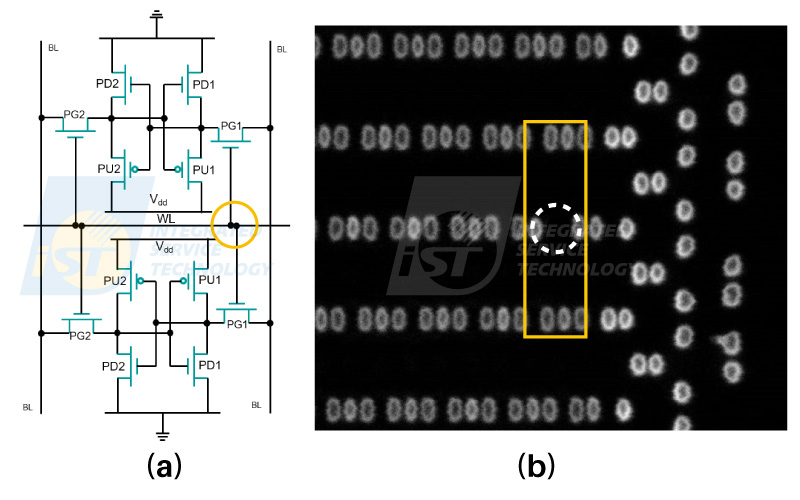

SRAM单一位元(bit)可由六个(6T)、八个(8T)、十个(10T)晶体管所组成,每个位元甚至也有使用更多晶体管的设计以实现多埠(Port)的读写功能,其中,以6T SRAM架构最为常见。6T SRAM由六个晶体管组成(图一),分为2个PMOS的Pull Up(PU),4个NMOS的Pull Down(PD)及Pass Gate(PG),这里PU和PD形成一个反相器,兩对PU与PD构成的两个反相器利用线路形構成互鎖結構,实现数据的保存。PU也称为Load Transistor,负责实现节点的高电位,即1的状态,PD也称为Drive Transistor,负责实现节点的低电位,即0的状态,在一个bit中,透过两个节点(Q和Q)高低电位互换,就能实现0和1两种状态的存储,PG也称为Access Transistor,负责实现位线(Bit Line, BL)讯号的接入,以实现读写功能。

6T-SRAM做读写动作时都需打开字线(Word Line,WL),如果要将数据写入,则要将位线(BL)及BL固定在一组固定的电压,强制 bit-cell内储存数据的节点 Q 及Q转换状态。当欲写入1时,BL电压为组件中的工作电压(Supply Voltage for the Drain,VDD),BL电压为0;而想写入0时,BL电压为0,BL电压为 VDD。写入动作是利用外部电压源强行改变bit-cell (Q,Q)的内容 (由外部影响内部)。

至于读取数据时,一样要将WL打开,即将 WL 拉到 VDD。和写入动作不同的只是BL和BL的状态。读取前,需将BL和BL的电压拉到相同的电位,也就是 V(BL)=V(BL),称为 pre-charge voltage,一般多为 VDD 或 (VDD – VT)。读取的动作是将外部BL及BL平衡(pre-charge),然后让bit-cell(Q, Q)的内容去影响BL和BL(由内部影响外部)。由于bit-cell的驱动力很小,需要仰赖感测放大器(sense amplifier)来放大BL及BL的差异,以读取出0或1。

二、常见的SRAM失效模式

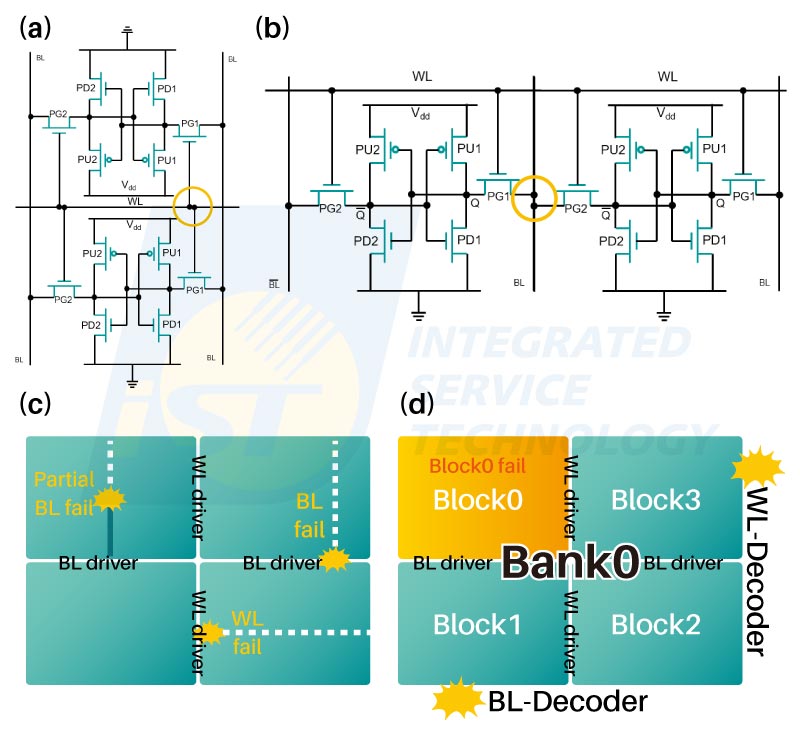

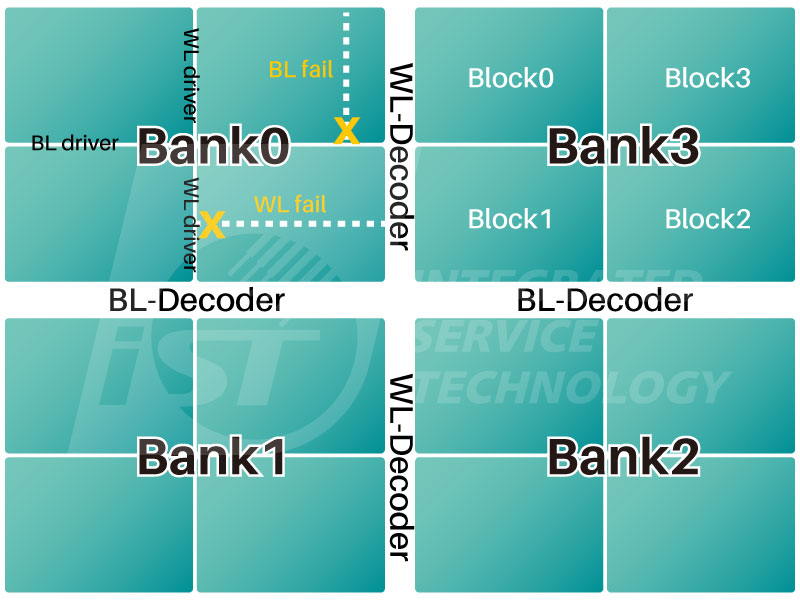

根据上一节SRAM操作原理介绍,我们可以SRAM异常点出现的位置,将SRAM的失效模式分成以下多种常见的失效模式:单位失效(Single bit failure)、双位失效(Twin bit failure)、四位失效(Quad bit failure)、部分位线失效(Partial bit line)、位线失效(Bit line failure)、字线失效(Word line failure)、区块失效(Block failure)等(图二)。在进行失效分析之前,宜特科技建议,如果能先确认失效位的失效模式,将可加速后续的分析进展。

(一)单位失效(Single bit failure):

单位失效又可细分为恒态单位失效 (hard single bit)与瞬时单位失效 (soft single bit)两种失效模式。恒态单位失效,是指该位在不同电压下都无法正常运作;瞬时单位失效 (soft single bit)失效,则指该位仅在特定电压下无法正常运作。

如一开始介绍,PU、PD或PG是构成SRAM的基本组件,Hard single bit的异常真因会落在PU、PD或PG的组件异常运作,或是连接这些组件的线路上。而Soft single bit的失效成因,则以PU、PD或PG组件微漏电或高阻值异常,甚或是各对PU、PD或PG之间电压值差异所导致。

(二)双位失效与四位失效(Twin and Quad bit failure):

当发生双位或四位失效时,因其为相邻位遭受功能失效异常,我们可以专注在失效位共享的线路上进行分析检测,常见的异常通常是其共享线路上金属层串接异常所导致。

(三)部分位线失效(Partial bit line):

此失效模式是指该位在线,部分位操作正常,但其他使用同一条位在线的位无法正常运作,这部分常见的失效真因是位线在正常与异常位转换交界处发生线路异常。

(四)位线失效(Bit line failure):

此故障模式与部分位线失效类似,但其发生异常的真因位置是落在SRAM 数组旁的位线控制电路,而非在SRAM数组之内。

(五)字线失效(Word line failure):

此故障模式与位线失效类似,只是发生在字在线,但往往发生异常的真因位置是落在SRAM 数组旁的字线控制电路。

(六)区块失效(Block failure):

此故障模式与位线或字线失效类似,但因其异常是整个区块失效,异常真因位置是落在SRAM 数组旁控制该区块的控制电路之上。

三、常见的SRAM失效模式失效分析手法

接着,宜特专业团队将针对上述列出的SRAM失效模式一一介绍各自的失效分析手法。

(一)单位失效分析方式:

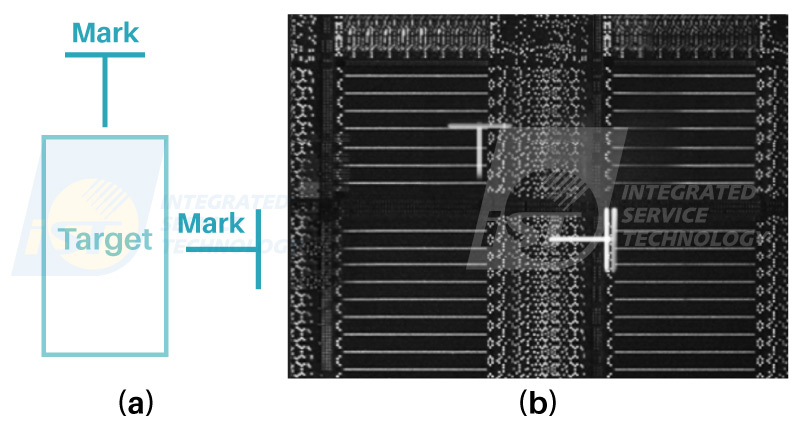

当遇到此类异常时,宜特科技失效分析实验室会先将试片去层至相关电路层次(如Metal3)进行芯片电路修改失效位元标示作业(图三),以便后续失效位定位更加精准。接着,我们会利用扫描式电子显微镜 (SEM)和导电式原子力显微镜 (C-AFM)从影响该SRAM功能失效电路架构的最上层电路层次开始逐层搜索。若后段制程中的金属层被排除异常,我们可以再利用奈米探针电性量测( Nano Prober)针对PU、PD或PG的组件特性进行电性量测,根据SEM与电性量测结果进一步评估后,可以考虑进行后续的芯片电路修改或穿透式电子显微镜 (TEM) 分析,以呈现相关物性异常,以利后续的真因改善作业。

(二)双位失效与四位失效分析方式:

当遇到此类异常时,我们会先将试片去层至相关电路层次(如Metal 5)进行芯片电路修改标示作业,好让后续失效位定位更加精准。接着,我们会利用SEM和C-AFM从该SRAM电路架构的最上层电路层次开始逐层搜索。我们可以利用SEM和C-AFM分析手法针对失效位共享的线路进行分析检测,并搭配后续的芯片电路修改或穿透式电子显微镜 (TEM)分析将真因呈现。

(三)部分位线失效分析方式:

在去层分析之前,此失效模式可先利用激光束电阻异常侦测 (OBIRCH) 和砷化镓铟微光显微镜 (InGaAs) 进行亮点定位,以再确认物性异常位置; 其后,再依上述去层、芯片电路修改定位与分析手法进行真因追踪。

(四)位线失效/ 字线失效/ 区块失效分析方式:

这些失效模式都与SRAM周边控制电路(Peripheral circuit)相关。此类异常可先利用OBIRCH和InGaAs进行亮点定位,再依亮点位置进行去层,并搭配SEM、C-AFM和Nano Prober分析手法进行异常点确认,再以后续的芯片电路修改或TEM分析呈现真因。

四、SRAM失效分析案例分享

(一)恒态单位失效(hard single bit)失效分析案例 :

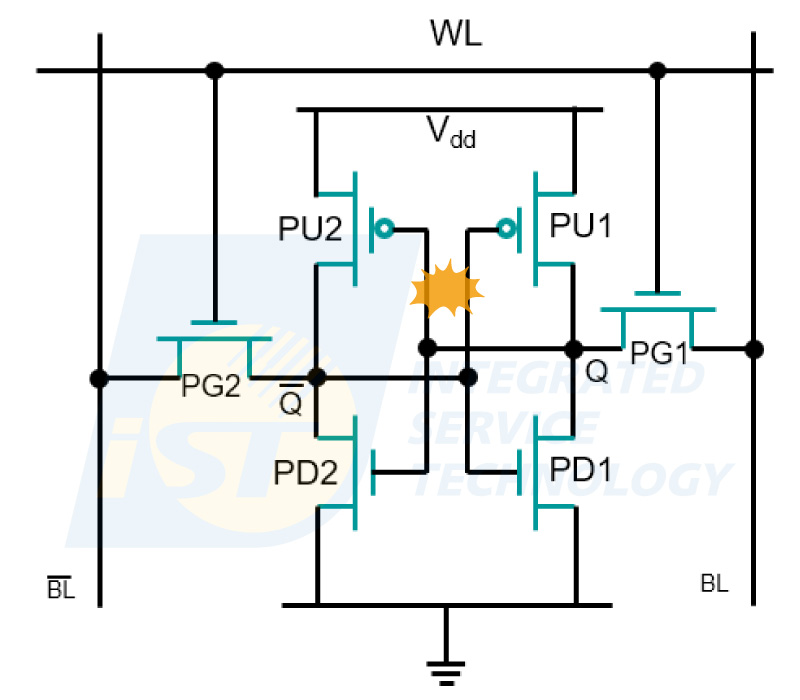

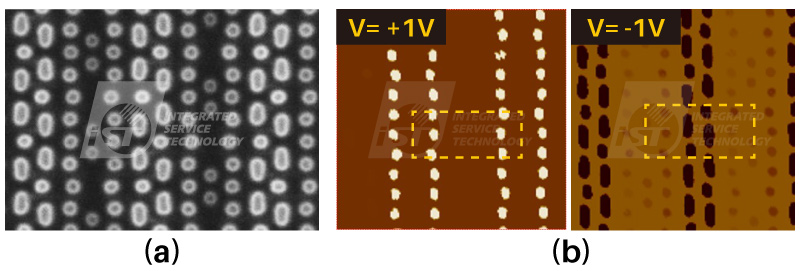

在这个恒态单位失效的例子中,将PD1与PU1串接起来的结构(Butted contact)和将PD2与PU2串接起来的结构有互相短路的现象(图四),因为这两个串接结构属同样电气性质,于SEM VC与C-AFM皆无法观测到其异常(图五(a)(b))。在这个案例中,我们使用Nano Prober进行两个结构对点,便可发现此两个原不应相连的电路结构有互相短路的现象(图六)。

(二)瞬时单位失效(Soft single bit)失效分析案例 :

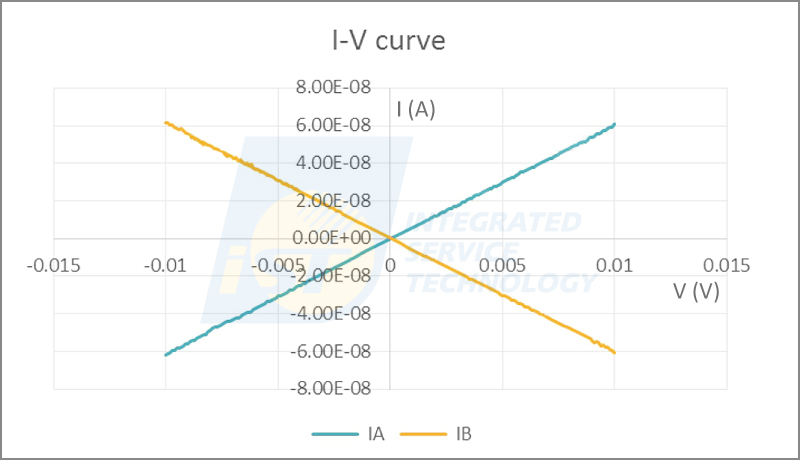

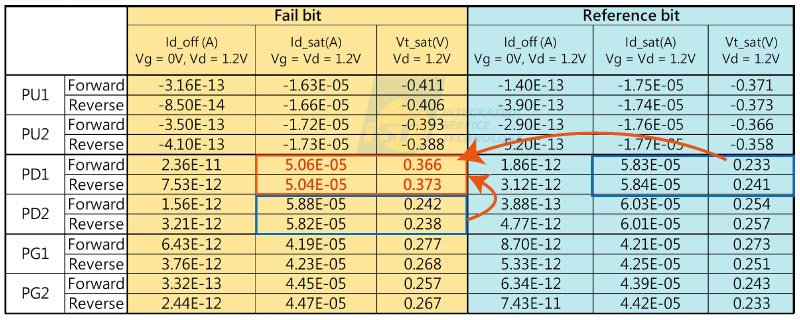

在这个瞬时单位元失效案例中,SRAM单元内的两组反向器因开关电压不一致,导致瞬时单位失效。这种情况下,我们无法透过SEM VC进行异常侦测。此时,我们使用Nano Prober对SRAM内的六个晶体管组件进行各自的电性量测。结果显示,失效位在其PD1的阈值电压较正常晶体管偏大超过100mV。经过电路设计者将该量测数据回馈到电路仿真后,验证了该阈值电压的明显差异确实可造成此瞬时单位失效异常(图七)。

在解析一个产品SRAM的失效分析中,发现总是无法找到故障异常点时,我们必须再度确认是否有位电性位置(electrical address)与位物性位置(physical address)不匹配的状况。此时,宜特科技失效分析实验室会建议进行Scramble check作业来验证和确认位位置的电/物性转译。

Scramble check,主要应用于新产品开发初期的验证。经过与电路设计者讨论后,选取特定的字线或位线甚或特定位,利用FIB芯片电路修改手法将其切断以制造失效位置,再利用产品测试程序进行失效位置确认,进而确认位电性位置(electrical address)与位物性位置(physical address)如何匹配。在Scramble check验证后,将可排除 SRAM 产品失效分析时找不到正确分析位置的可能性。

本文与长久支持宜特的您分享,本文与长久支持宜特的您分享,如果有需要SRAM失效分析流程表,欢迎与我们联系,宜特将提供一张精心制作的图表,供您参考。欢迎洽询 +886-3-579-9909 分机 6775施先生(CY) │Email:web_ISE@istgroup.com;marketing_tw@istgroup.com。