发布日期:2024/10/09AI高速信号

发布单位:iST宜特

随着 AI 技术不断进步,如何确保高速信号在AI应用设备中传输时,仍能保持稳定,且不受干扰,是许多工程师面临的挑战。如何透过最新AI高速信号全面解决方案,确保产品顺利通过高速规格验证,在这波技术浪潮中保持领先?

AI高速信号

在当今的技术环境下,无论是 AI 服务器、加速运算卡、交换器,还是 AI 边缘运算设备如 PC、游戏主机、绘图卡、机顶盒、监视器及电视等,所有这些设备都需要面对高速信号传输的挑战。从信号的干扰排除到材料的选择,每一个设计环节都可能影响最终产品的性能和市场表现。特别是 PCIe Gen 6、Ethernet 400/800G 等高速规格的普及,让产品测试与验证成为设计过程中不可或缺的一环。市场上许多企业,尤其是涉及 AI 应用的开发者,迫切需要高效的测试方案来解决高速传输中的潜在问题,并确保产品能顺利通过市场验证。

本文iST宜特信号测试实验室将以实际案例,分享如何透过最新AI高速信号全面解决方案,从前端设计仿真评估、电路板(PCB)特性分析、埠物理层 (Port Physical Layer,简称PHY) 测试验证,与客制化治具设计等,一站式协助您在这波技术革新中保持领先。

AI高速信号

AI高速信号

iST宜特信号测试实验室从实际工作中发现,AI应用下更高速的运算环境,除了对信号传输的稳定性、除错需求及散热管理产生新的挑战,亦引发一系列的技术难题,从高速信号中继IC (Re-driver) 做信号补偿/信号重整的导入需求,到电路板材料的升级,甚至到传输线材与连接器规格的提升,产品设计与测试面,皆面临更多的困难与要求。以下我们将一一为您介绍最新AI高速信号四大核心解决方案:

一、前端设计模拟与评估

在高速信号传输产品中,信号完整性(SI)和电源完整性(PI)仿真是确保产品竞争力的关键。随着电子技术进步,特别是在AI高带宽应用中,阻抗不匹配、结构设计不良或Via排布不合理,易引发信号间干扰、串扰、失真及延迟,影响信号质量。随着指令周期和密度提高,高频切换与大电流会导致电压波动和噪声,进而影响电源完整性及系统性能。因此,SI和PI评估至关重要,可确保系统在高速运行下的稳定性。

iST宜特信号完整性 (SI) 以及电源完整性 (PI) 的模拟服务,客户只要提供线路图与Gerber 相关档案,透过Ansys & Cadence 仿真软件,即可在产品开发阶段,协助客户执行前端设计评估;在试产前期,进行信号仿真,协助客户降低因设计缺陷所带来的成本风险。

(一) iST宜特提供的服务项目

1. 信号完整性 (Signal Integrity,简称SI):

- (1) S 参数:反射损耗(Return loss)/ 插入损耗(Insertion Loss)/ 串扰(Crosstalk)

- (2) TDR 时域反射

- (3) Eye Diagram眼图分析

2. 电源完整性 (Power Integrity):

- (1) DC IR-drop 分析:分析 Power Net 压降,确保不超过允许范围,以避免系统异常。测试指针包括压降分布、电流密度、DCR (Direct Current Resistance,直流电阻) 和功率损耗。

- (2) AC PDN (Power Delivery Network) 分析:检查设备端阻抗,确保维持低 AC (Alternating Current,交流电) 阻抗。高阻抗可能导致 IC 运作异常和电源噪声,影响系统稳定性。

(二) 宜特案例分享:

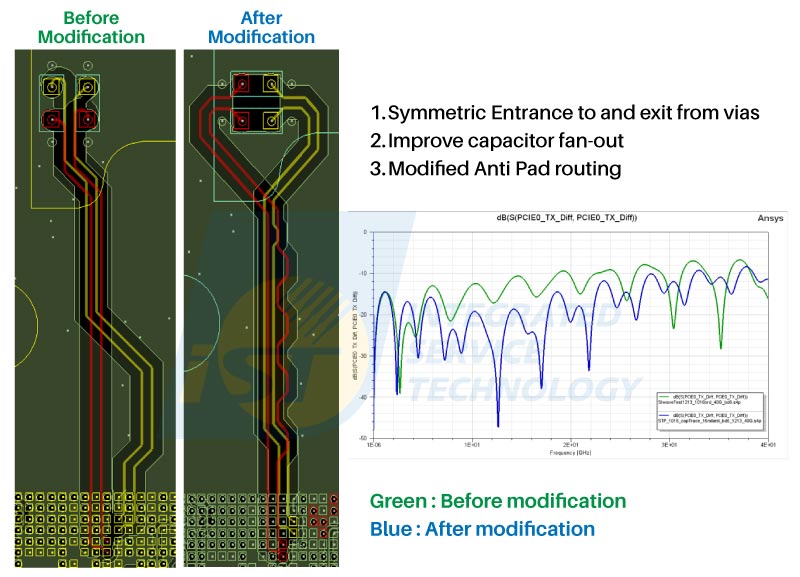

1. 案例一:Layout优化分析

在完成Layout设计后,我们进行了SI分析以确认信号质量。在仿真过程中发现,信号在工作频段(基频8GHz)有较高的反射率,特别是在走线进出Via处及电容附近存在改善空间。我们针对这些区域进行了优化,让Via走线对称化,并改善电容下方的Anti Pad routing,解决了电容过大导致的阻抗不连续问题。经过调整,基频及倍频的反射率显著降低,确保了信号完整性。2. 案例二:DC IR-drop改善

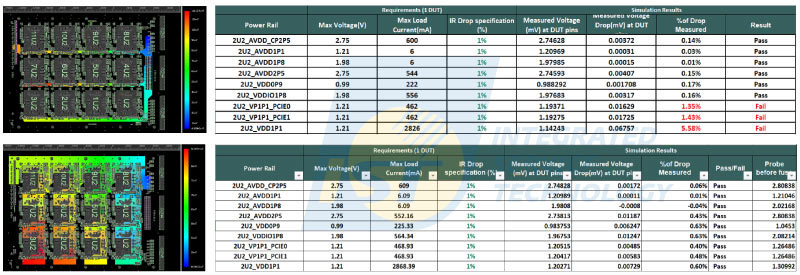

客户在设计板子时,遇到了随着传递距离增加而造成的电压损耗过多的问题。通过Power DC模拟结果分析,我们观察到Power Plane上的压降过高,进一步检查后发现Power Plane过于破碎是主因。针对这一问题,我们调整了Power Plane的完整度与分布,降低了整体压降,并优化了Sense补偿位置及方式,最终达到客户对各Site压降差异的需求。二、PCB板材特性测试

在高速信号传输的环境下,损耗越来越大,PCB 使用的板材对信号质量的影响变得尤为重要。为了确保印刷电路板(PCB)的板材质量符合标准,不仅在设计时间需要进行评估,还需透过实际测试来验证其性能。

(一) iST宜特可提供印刷電路板(PCB)及印刷電路板組裝(PCBA)的測試項目:

1. 阻抗测量(Impedance Measurement):测试PCB材料的阻抗特性,确保信号传输的稳定性。

2. S参数测量(S-parameter Measurement):分析高速信号的传输质量。

3. Intel Delta-3.0/4.0 测试(Intel Delta-3.0/4.0):在正常温度及变化温度下(Temp. Normal/Variation),验证PCB在不同温度条件下的性能表现。

4. 板阶除错测试(Board Level Debug):进行端到端通道损耗测试(End-to-End Channel Loss),找出并修正电路板信号传输中的问题。

(二)宜特案例分享:

1. 案例一:TDR / S-parameter

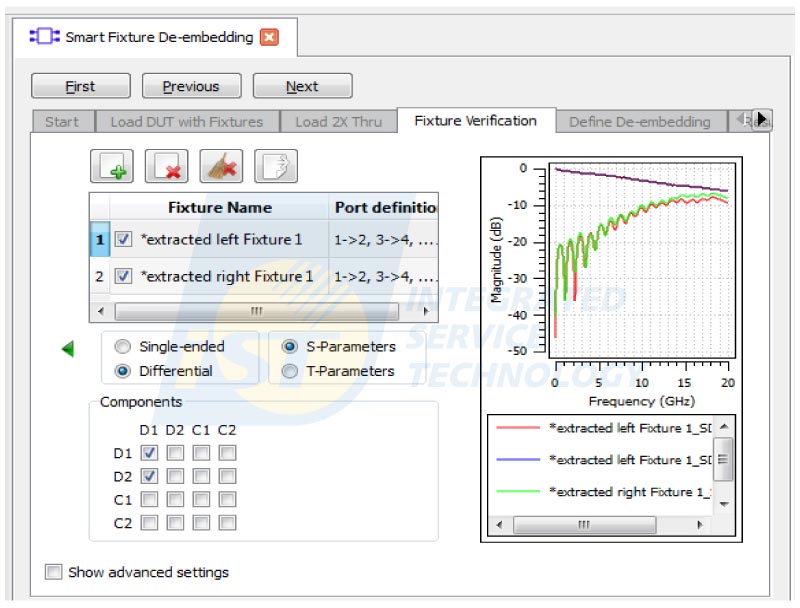

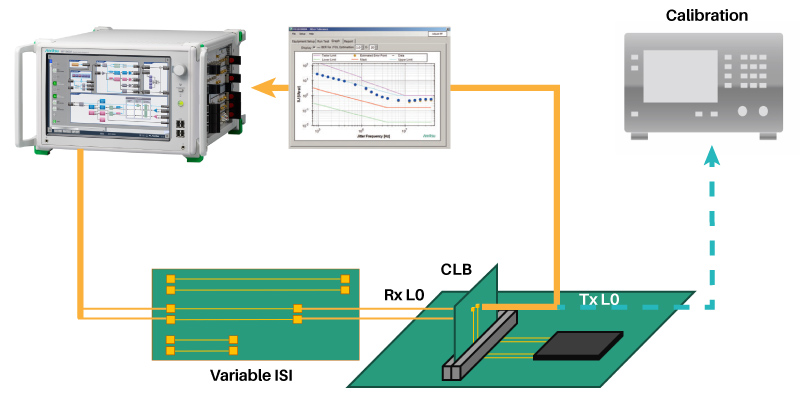

当客户的信号验证结果未能符合协会规范时,我们建议针对 PCB 进行 TDR(时域反射)及 S-parameter 测试,以确保 PCB 板的设计阻抗和生产过程符合设计要求。2. 案例二:Fixture De-embedding

在测试 PCB 特性时,探棒或治具会增加额外的损耗。为了消除这些影响,我们使用软件进行去嵌化处理(De-embedding),以获取更准确的测试结果。三、埠物理层一致性测试 (PHY Conformance)

PHY (Port Physical Layer)是网络协议中的端口物理层,负责数据在设备与网络或其他设备间的传输。PHY Conformance用于测试设备的物理层是否符合特定协议的技术规范,确保其能稳定、有效地传输数据,避免信号失真或干扰。

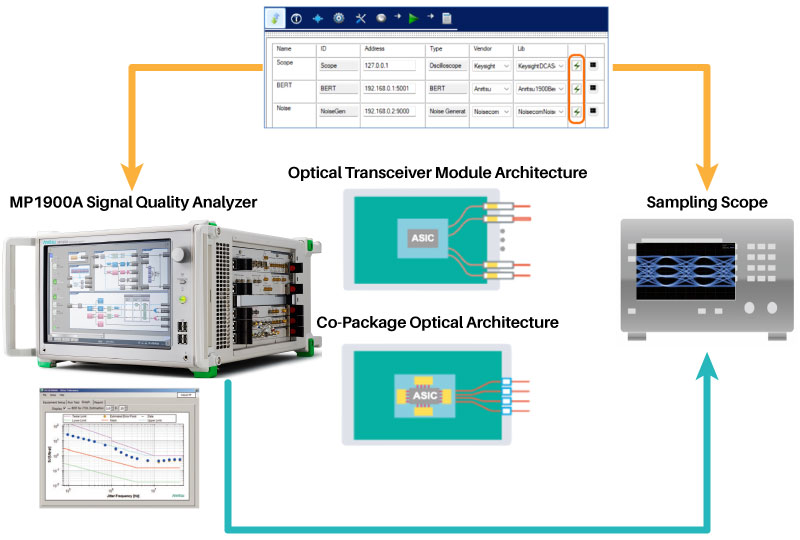

客户只需提供半成品板和接口数据,即可进行测试验证,协助客户在硬件或是系统层面符合特定标准,确保其正常运作,并满足规范要求;同时也可以进行故障诊断与排除(Debug)服务,确保产品顺利运行。

(一)iST宜特提供的PHY Conformance测试,涵盖PCI-E(Peripheral Component Interconnect Express) 和以太网 (Ethernet) 领域:

1. PCIe 5.0/6.0 预符合性测试(Tx/Rx/100M Clock):测试PCIe 5.0和6.0的传输性能,确保其符合预定的时序和信号完整性要求,包含PCIe电器特性(PCIe Electrical Test)与协议测试(PCIe Protocol Test)。

2. Ethernet 400/800G 符合性测试(IEEE 802.3bj/bs/ck):验证Ethernet 400G和800G的性能是否符合援QSFP-DD及OSFP等高性能光纤模块标准,确保其在高速数据传输中的可靠度。

四、客制化测试治具设计

高速信号测试过程中,客制化测试治具除了可提升测试效率、缩短开发周期,还能避免不合适治具导致的测试误差,确保产品的高性能与可靠度。iST宜特可根据客户需求,设计专属的测试治具,并提供从计划、设计、测试验证到生产的一条龙服务,确保测试设备的效果和符合特定要求。

生成式 AI 的兴起,加速了高速信号市场的成长。iST宜特信号测试实验室凭借多年来累积的高速信号测试经验,结合业界顶尖设备,与全球标准组织如 USB-IF、HDMI 协会及 VESA 建立了紧密的合作关系,为您提供最精准的测试和分析。不论您是从事服务器、交换器、AI 加速运算卡,还是边缘运算装置如PC、游戏主机、绘图卡、机顶盒、监视器及电视等的设计开发,我们都能协助您迅速进入市场。

如果您对我们的服务有任何问题或需求,欢迎随时与我们联系。宜特信号测试实验室 +886-2-2792-2890分机2715 陈先生/David │Email: web_si@istgroup.com;marketing_tw@istgroup.com。