半导体IC不断演进就是为了有更快的指令周期、较低功耗及降低成本等需求,于是工艺技术的推进,概括可分为三大方向:

- 挑战摩尔定律,从28nm-16nm-10nm-7nm-5nm一路往更小的工艺推进

- 跳脱一般2D(平面)的框架,让芯片可以堆栈成2.5D或3D的架构

- 更有效率的进行功率转换及运用

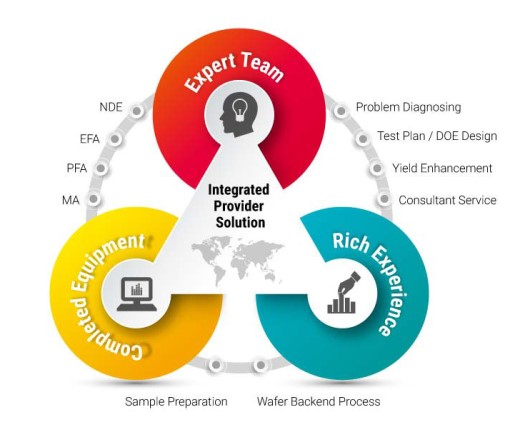

针对上述三大方向,宜特不只可以在客户产品发生失效时,协助客户在短时间内找到自身产品失效状况(failure mode)进而找出原因(Root cause),更进一步的为功率半导体客户提供晶圆后端工艺整合服务。

Step-by-step完成分析,找出失效状况

当产品失效发生(R&D 或 RMA)需进一步解析时,宜特拥有完整的失效分析平台,从非破坏式分析开始,如: 超高解析3D X-Ray、SAT超音波扫描;电性量测分析,如IV量测组件的特性比较;故障点的定位,如: Thermal EMMI、InGaAs、OBIRCH等。

之后加上完善的样品前处理技术,如: 样品前处理技术,包括 芯片开盖(Decap)、芯片去层(Delayer)、剖面/晶背研磨(Cross-section & Backside)、离子束剖面研磨(CP)等;搭配高解析之观察工具,如: 场发式扫描电镜(FESEM)、双束聚焦离子束(Dual Beam FIB)。

而在材料分析方面,具备材料微结构分析与奈米级表面成分分析能量,如欧杰电子能谱仪(AES)、X光电子能谱仪(XPS)、穿透式电镜(TEM)、二次离子质谱仪(SIMS)与EDS、EELS成份分析…等全方位分析技术,可解决客户在材料分析上的需求。

而在功率半导体芯片方面,宜特也透过子公司-「宜锦科技」提供晶圆后段工艺整合服务,让客户的晶圆在离开前段代工厂后,可以直接来到宜锦科技进行正面金属化工艺:化学镀 /无电镀 (Chemical / Electro-less Plating)、正面金属溅镀沈积 (Front Side Metal Sputtering Deposition);背面研磨工艺:晶圆减薄(Wafer Thinning/ Non-Taiko Grinding/Conventional Grinding)、太鼓超薄研磨 (Taiko Grinding);背面金属化工艺:金属蒸镀沈积 (Metal Evaporation for Backside Metallization) 、厚银工艺(Thick Ag Process)、背面金属溅镀沈积 (Backside Metal Sputtering Deposition)、电镀 (Electro-Plating),以及后续芯片测试 (Chip Probing)、雷射刻号 (Laser Marking)、芯片切割 (Die sawing) 等,宜特以一站式服务协助客户完成从晶圆到晶粒前的各项工艺步骤。

另外,企业导入先进半导体制程的目的,是进入国际电子大厂电子供应链,有鉴于国际大厂对于供应链厂商的要求除了产品规格精进外,也包括质量管理、环保管理与CSR。因此宜特也提供全面质量管理(IATF 16949辅导)、环安卫与 ESG 增值服务、与温室气体水足迹盘查协助半导体产业加速进入国际电子大厂之供应链。