发布日期:2025/2/18电路修补

发布单位:iST宜特

切错点、接错线,让你胃食道逆流吗?本期宜特小学堂,带您一次掌握FIB(Focused Ion Beam)电路修补全攻略!帮助工程师跳脱debug地狱,高效完成设计验证。

电路修补

在芯片设计这条路上,就算模拟结果看起来完美得像神作,一上芯片还是可能冒出让人崩溃的电路异常。这不只是花钱重投片的问题,更是会把项目时程拖到天荒地老,客户追杀。更惨的是,碰到电路有问题时,工程师最常面对的困扰就是:找不到defect,完全搞不清楚要接哪条线、切哪个位置,debug起来简直让人怀疑人生。

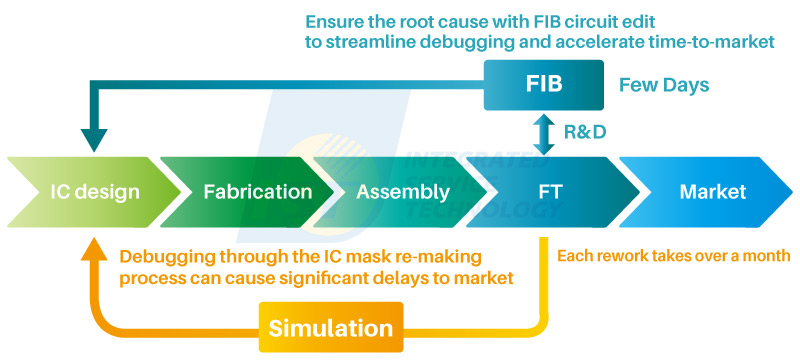

这时候,FIB(Focused Ion Beam)电路修补技术就像救世主一样登场了!它可以快速又灵活地帮你修电路,用最少的成本和时间完成设计验证,不再掉进无限循环的debug地狱。

作为台湾首家推出FIB电路修补服务的民营实验室,宜特科技FIB电路修补服务,可节省每颗芯片在设计时间三到六星期的研发时间,并节省上千万重新下光罩的经费,让产品可以快速上市。宜特FIB实验室更以24小时全年无休的服务,协助客户产品除错,快速找出问题症结。

之前的宜特小学堂,我们分享了如何进行先进工艺芯片的FIB(Focused Ion Beam)电路修补,介绍了晶背修改的多项优势,也展示了一些高难度的修改案例(阅读更多:先进工艺的芯片,该如何从晶背进行FIB电路修补? 和 5奈米芯片FIB电路修补 到底难在哪)。本期宜特小学堂,我们将不藏私分享宜特30年的FIB电路修补经验,帮助您全面了解这项关键技术,让debug加速跑,设计效率也跟着直线飙升!

电路修补

电路修补

一、FIB 原理简介

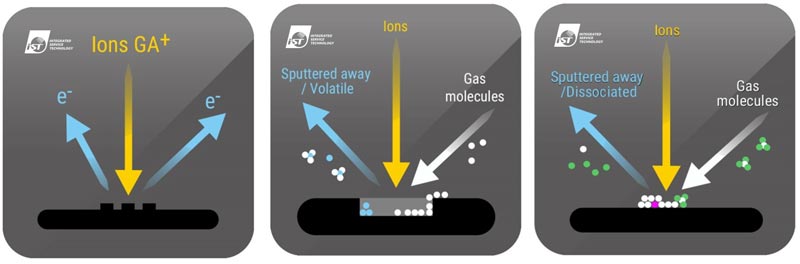

FIB (Focus Ion Beam)聚焦离子束电子显微镜,是利用镓(GA+)离子源透过电场牵引成离子束,收集高速碰撞样品表面产生的二次离子、电子后成像;在离子轰击过程中利用不同气体的注入,对芯片上各种材料进行选择性地加速或减缓蚀刻,以及沉积导电和介电绝缘材料,达到修改电路的目的,搭配CAD导航系统辅助,准确的定位目标,提高电路修补精准度。

二、为什么要进行FIB电路修补?

就像医生透过外科显微手术精确地解决病人的身体缺陷,改善其健康状况,宜特FIB实验室透过专业和细致的芯片电路修补,能有效地在芯片下线(tape out)前确认问题所在,可节省高额重新投片成本,加快原型验证的速度,缩短上市时间。FIB电路修补技术也可协助客户在开发时程紧迫的情况下,进行少量改版量产,再将样品送交终端客户进行验证,成功取得先机,争取到订单。

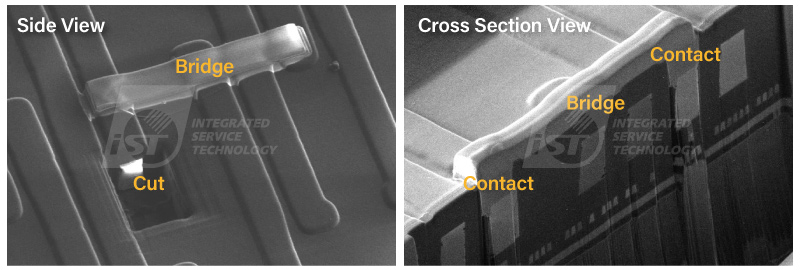

FIB技术利用蚀刻移除绝缘层及金属层,并透过沉积金属材料重新连接到其他路径,这一过程能够精确地依照客户需求,并进行测试确认电路中的问题。

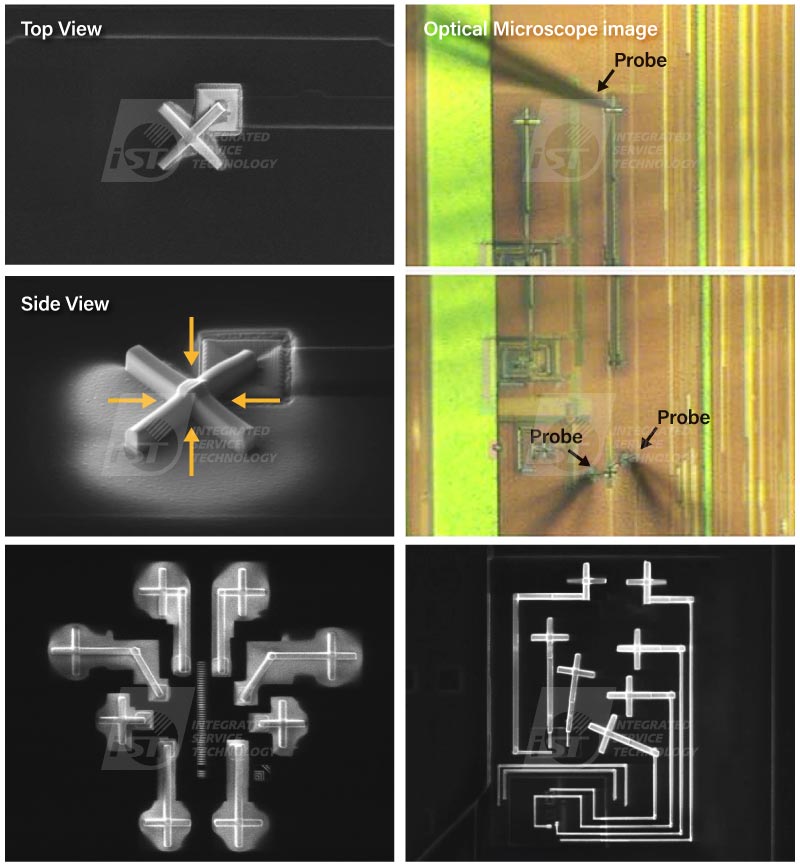

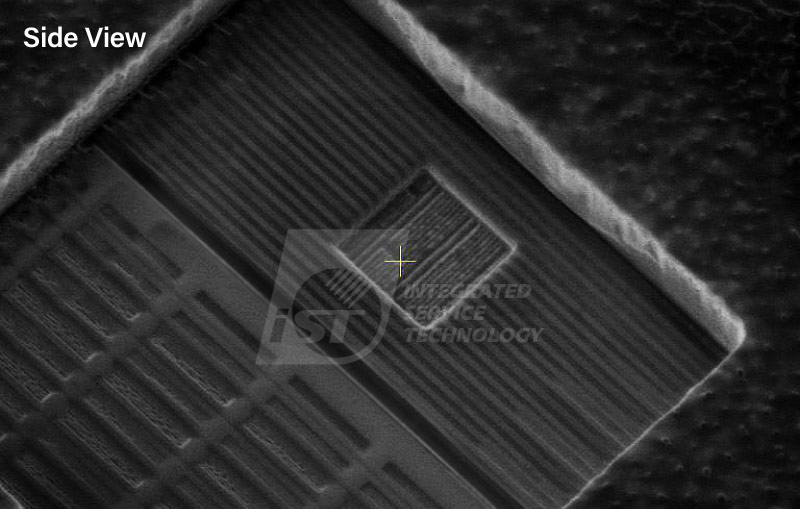

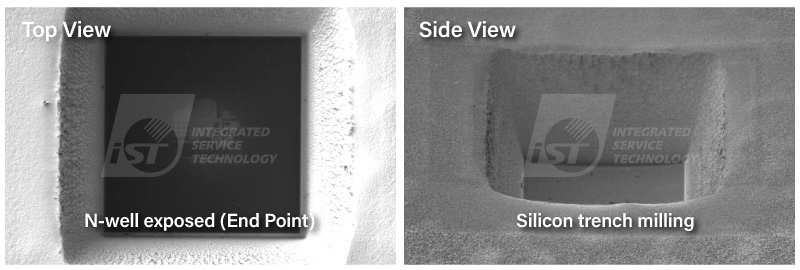

透过剖面图(Cross-section view),我们可以清楚地了解使用聚焦离子束这一技术能够精确去除表层材料,暴露出目标区域的金属层,紧接着将金属材料沉积填充在接触点(contact)上并在芯片表面进行桥接,实现电路的重新连接。后续便可进行测试,真实验证电路的功能是否符合仿真结果。

此外,根据条件的需求,也能执行更复杂的电路重构,进一步扩大解决方案的范围,客户依据测试结果确认电路中的缺陷,满足在电路除错上的各种需求。

三、宜特FIB电路修补的各种广泛应用

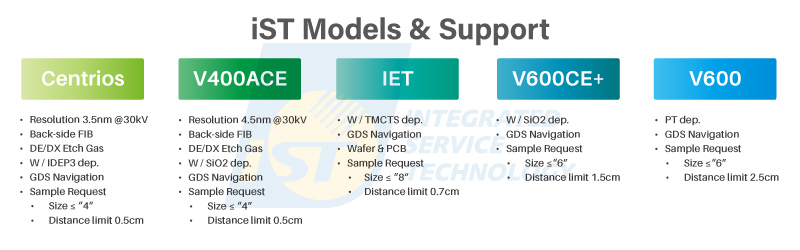

宜特的FIB电路修补技术已突破3nm工艺,并提供芯片正面与背面电路修补服务。设备类型多元且数量充足(表一),不仅能满足高产能需求,还能灵活提供多样化解决方案,确保稳定的高良率与快速交期。此外,宜特拥有丰富经验的技术团队,专精于多种设备操作,并独家支持8吋晶圆不破片的电路修补服务,这项技术是台湾市场中的唯一选项。

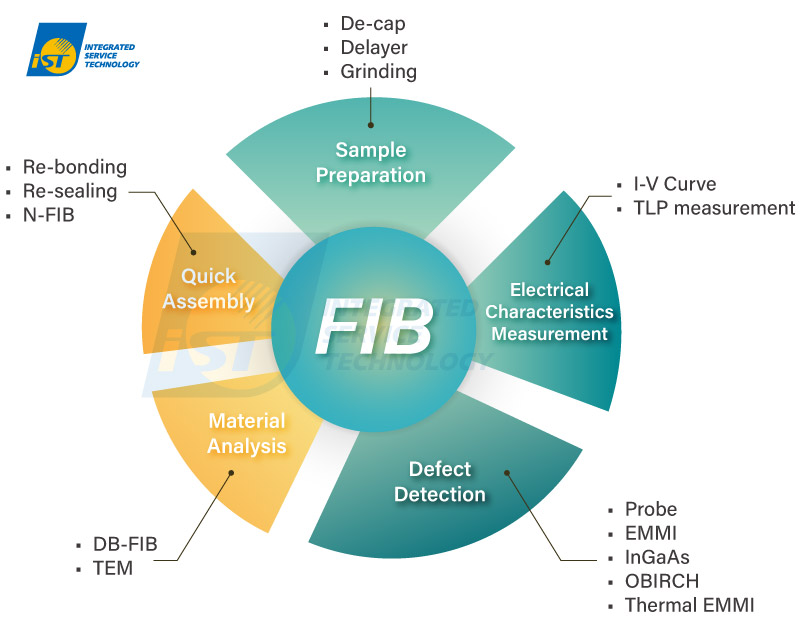

由图五可见,FIB电路修补后可接续进行电性量测、故障点侦测、材料分析和快速封装等实验,以下我们将一一分述FIB的各种广泛应用。

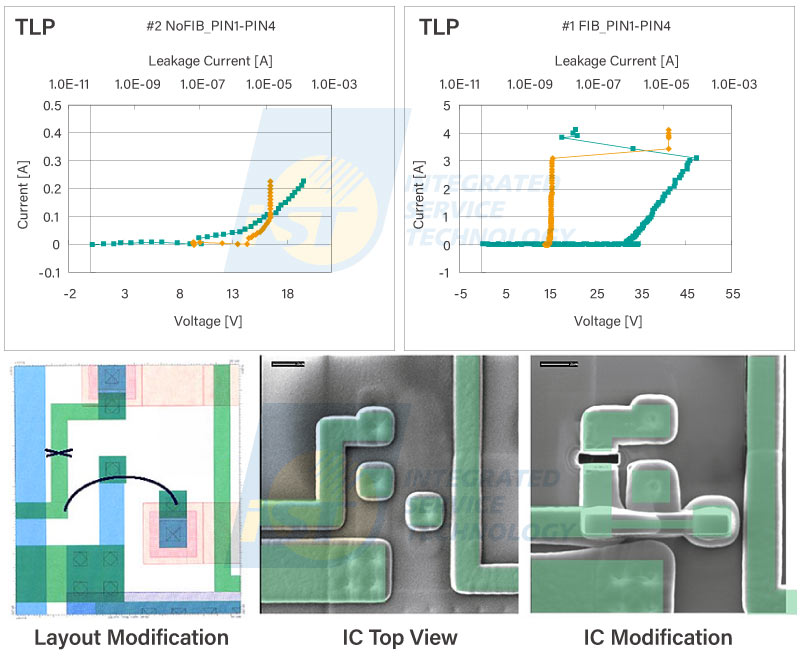

(一) 利用FIB技术沉积金属材料进行电阻调整

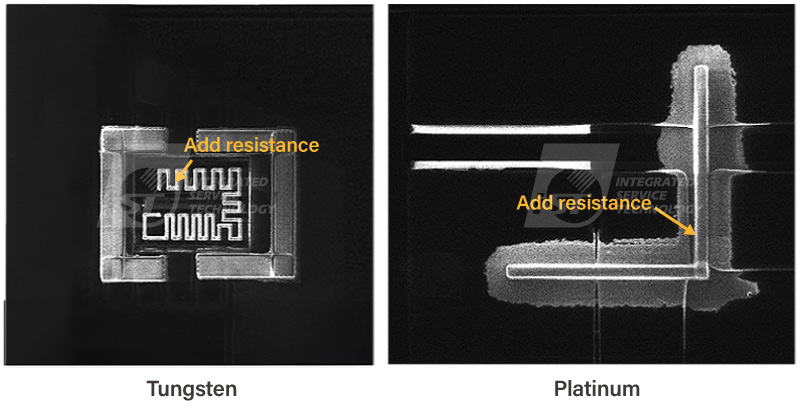

FIB 电路修补技术可以利用沉积金属材料进行电路连接,然而,进一步的应用,亦可以根据客户需求,在两个电路节点之间,透过沉积具有不同电阻系数的金属,例如钨(Tunsten)或铂(Platinum),来控制金属的连接长度,达到调整电阻值的目的。此法可用来仿真不同电阻对电路性能的影响,后续亦可以进行波形(I-V Curve)、ESD等相关故障分析实验量测。

(二)宜特独特客制化的FIB PAD设计帮助芯片后续顺利进行电性测试

宜特的FIB Pad设计为十字形状,除了能够使探针稳定地顶住任一内角,防止针座滑动,并且拥有多向角度调整的可能性,方便在接触不良时,重新调整针座位置与方向以达到最佳接触效果,进而重复使用。不仅提高了操作的稳定性,也延长使用寿命。

并可进一步根据客户需求制作更多且更复杂的FIB Pad,利用点针技术准确地撷取讯号,测试该区域电路是否符合研发设计要求,及时发现进而定位缺陷,后续可再进一步进行电路修补,改善问题;或是接续亮点分析,针对异常位置进行剖面(cross section) FIB或TEM分析,确认工艺缺陷。

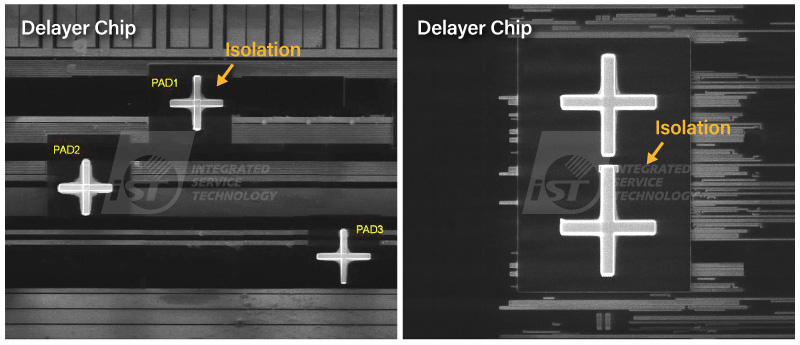

此外,宜特的FIB 实验室建置介电绝缘材料,即使是晶圆半成品或经过delayer处理的芯片,依然可以先利用绝缘材料将暴露的金属层隔绝,从而安全地进行FIB加工。

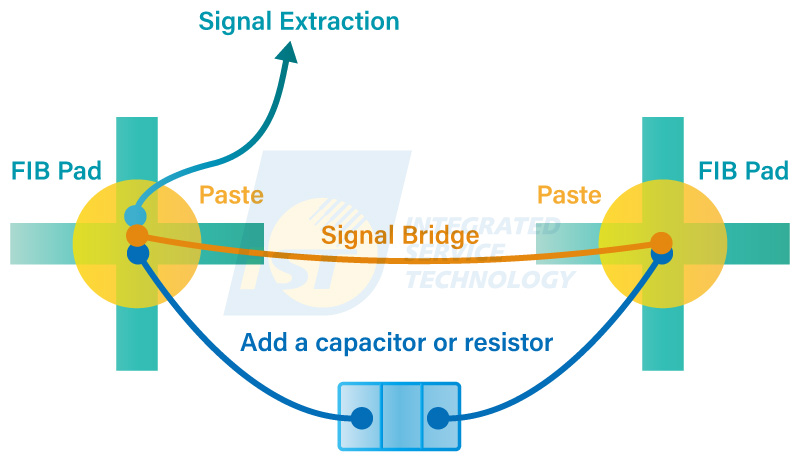

(三)FIB Pad 延伸应用:新型 FIB 电路修补(N-FIB)

1. 低阻抗解决方案

以1,000um的连接距离为例,使用传统FIB沉积技术,Pt材质的阻抗为6k Ω,W材质为2k Ω,而N-FIB技术则可实现仅10 Ω的低阻抗,显著提升效能。2. 讯号引出

取代传统探针测试,提供更高的灵活性与重复性,应用于更频繁与复杂的测试需求与环境。3. 添加电容或电阻

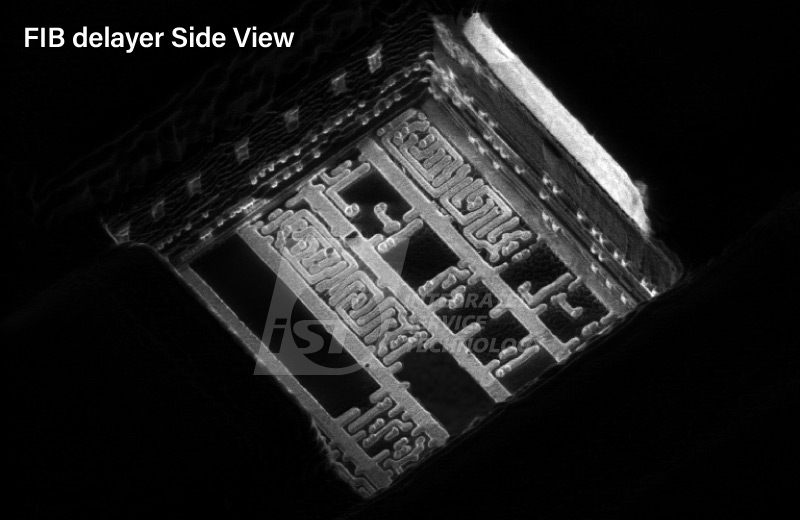

利用N-FIB技术连接电容或电阻,使用SMD 0201封装,尺寸为300*600um,实现更精确的电路测试需求。(四)FIB Delayer技术应用于故障分析Nano Probe测试

在测量先进工艺或高速讯号功能的芯片时,若使用FIB Pad方式进行测试,可能会因额外增加的阻抗或容抗而导致讯号失真。为了解决这一问题,可以使用宜特故障分析实验室建置的奈米探针电性量测(Nano Prober)设备,将损耗降至最低。

在此之前,须对芯片进行去层(delayer),然而传统的去层技术需要全面性的逐层研磨至目标金属层,这不仅耗时,且在面对先进工艺芯片时,过度研磨的风险也会相对增加。在这种情况下,FIB可以精确的锁定局部区域进行去层,大幅降低失败风险,FIB的蚀刻技术成为一个理想的解决方案。

(五)FIB晶背电路修补技术

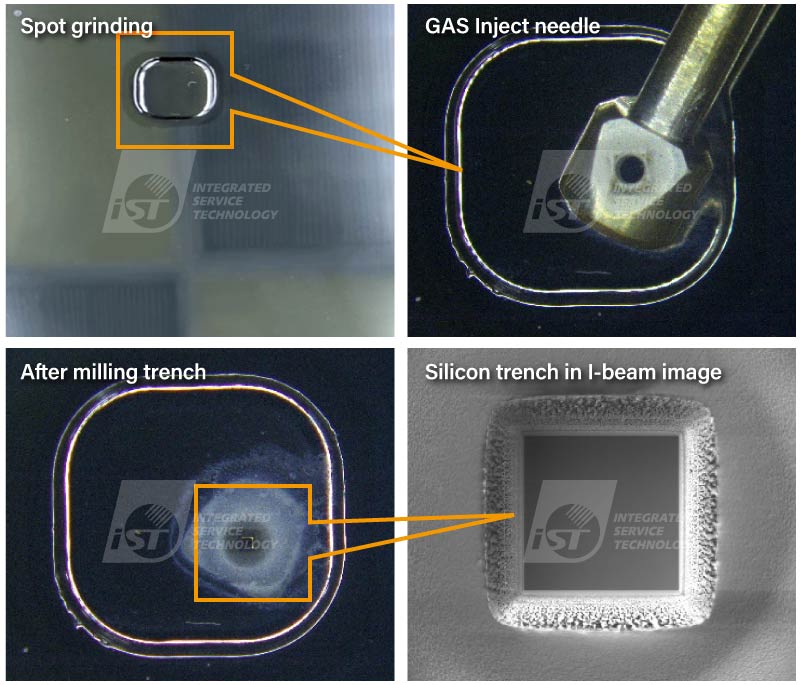

晶背电路修补技术是一项经过多年发展且相当稳定的技术,并且已经建立了完整的工作流程,包括开盖、研磨及重新封装等,都有对应的解决方案。在这一过程中,特别是针对目标区域进行局部研磨,将能够实现CoWoS封装中的FIB电路修补。

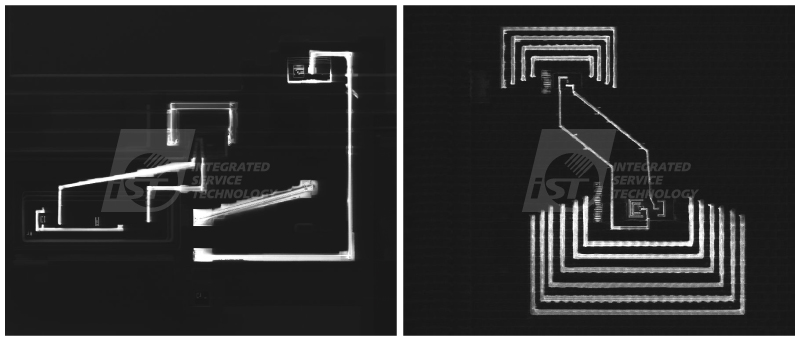

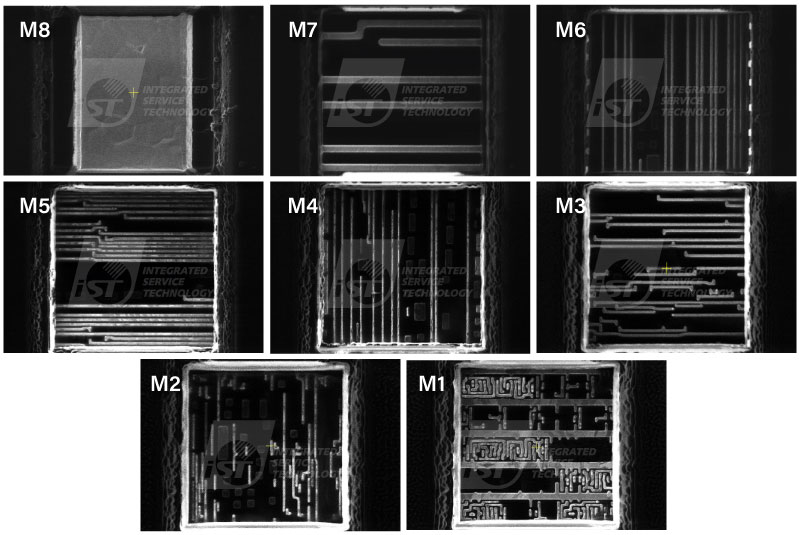

从晶背执行电路修补时,目标通常位在M1~M3的金属层,都是芯片最小设计尺寸金属层,往往考验着实验室人员的技术能力以及调校出的影像质量。参考图例展示,宜特利用设备最小beam current 1.2pA 调校高分辨率的影像,有助于电路判断进而提高电路修补成功率。

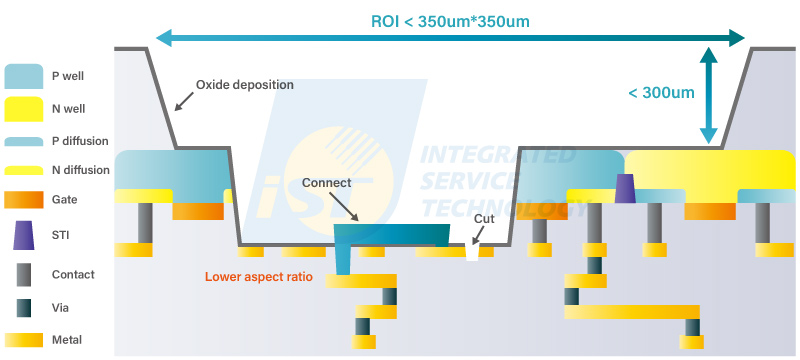

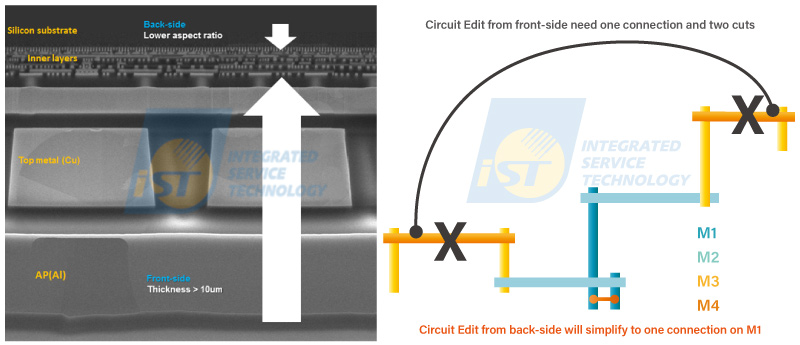

随着先进工艺组件尺寸的持续微缩,以及终端产品需求的不断推动,Flip Chip封装的应用范围逐步扩大,其中CoWoS(Chip-on-Wafer-on-Substrate)封装也采用了Flip Chip 2.5D封装形式。从FIB晶背施工的角度来看,Flip Chip封装具有低深宽比的优势,并且修改过程会先遇到电路源头,能够在一定程度上简化欲修改的内容。然而,随着工艺节点进入7nm、5nm、3nm,甚至未来的2nm,芯片的电路多样性与复杂度大幅提升。尽管我们已经展示过成功的3nm修改案例,但这些先进工艺所带来的挑战,大大提高电路修补的难度。无论是技术能力还是设备能力,都需要具备更高的要求。市场誉为黑科技的晶背供电技术(Backside Power Delivery Network, BSPDN),将成为FIB电路修补技术未来面临的一大挑战。

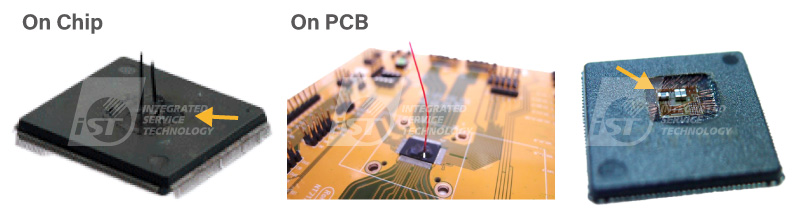

(六)FIB 技术应用于各种封装

宜特FIB实验室可满足市场大部分热门封装的FIB电路修补,以下将针对三种特别的封装,进行解析。

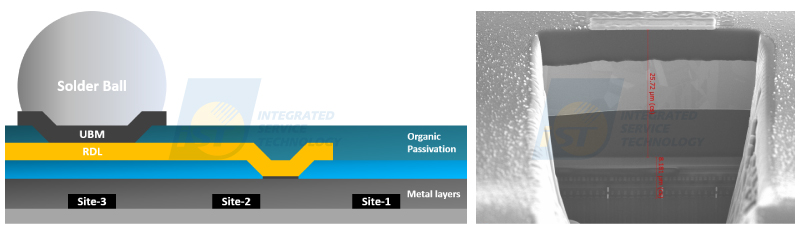

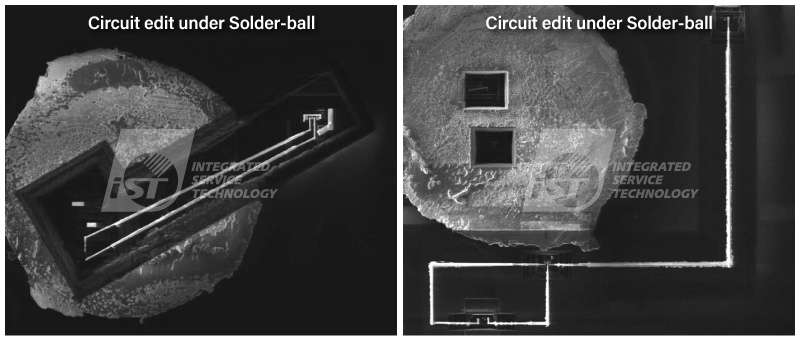

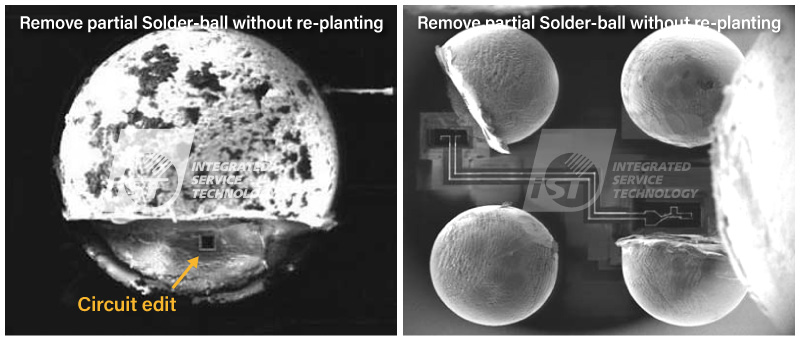

1. WLCSP (Wafer-Level Chip Scale Package)

宜特在2014年即提供WLCSP完整的解决方案,除了Site-1、Site-2皆可以执行电路修补外,针对Site-3更提供锡球局部移除与移除重植的方案,解决客户电路在锡球下无法执行FIB 电路修补的困境,同步提供FIB 晶背电路修补,并成功实现在同一颗样品上进行芯片正面与背面电路修补的案例。统计自2014年推出后共为全球客户执行超过10,000颗WLCSP的电路修补。

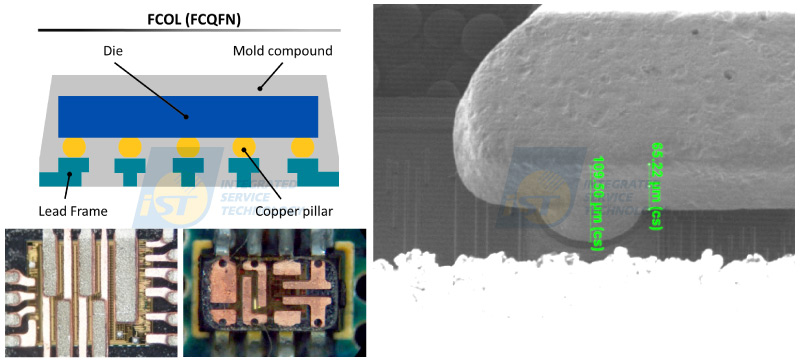

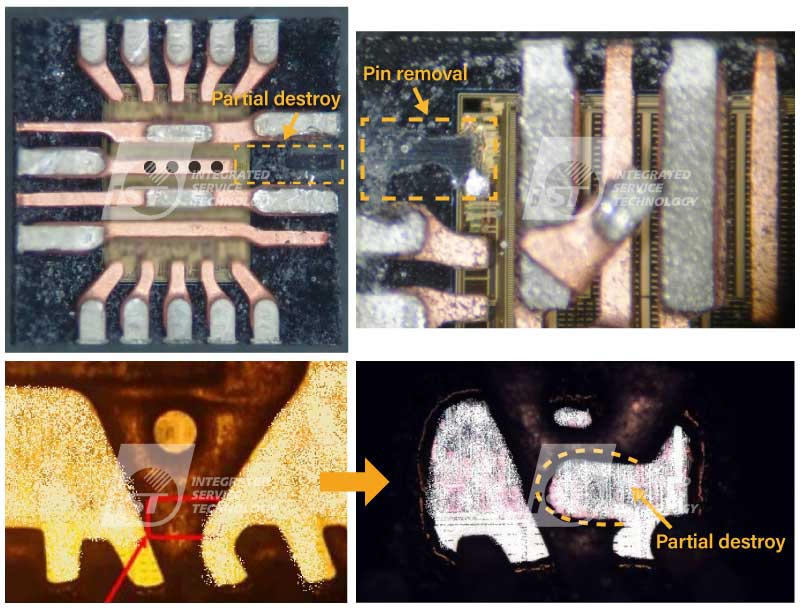

2. FCOL (Flip Chip on Lead)

FCOL封装技术通过利用铜柱和导线架取代传统的焊线,不仅缩小了封装尺寸,同时降低了热阻与电阻,进而提升了散热能力与电性效能。然而,芯片上方大面积的导线架却为FIB电路修补带来挑战,当目标区域被导线架覆盖时,将无法进行FIB修改。为解决这一问题,宜特在2014年提出了局部移除导线架的创新方案,该方法在保持芯片正常电性运作的同时,能够顺利完成FIB电路修补,需要注意的是移除封胶体后,裸露的导线架变得相对脆弱,因此在FIB完成后,必须进行封胶处理以增强结构稳定性。此外,必须提醒,一旦导线架被移除,将无法重建,这一点需特别留意。

宜特FIB实验室,针对FCOL封装产品,亦同步提供FIB 晶背电路修补,并且成功实现在同一颗样品上进行正面与晶背电路修补的案例。

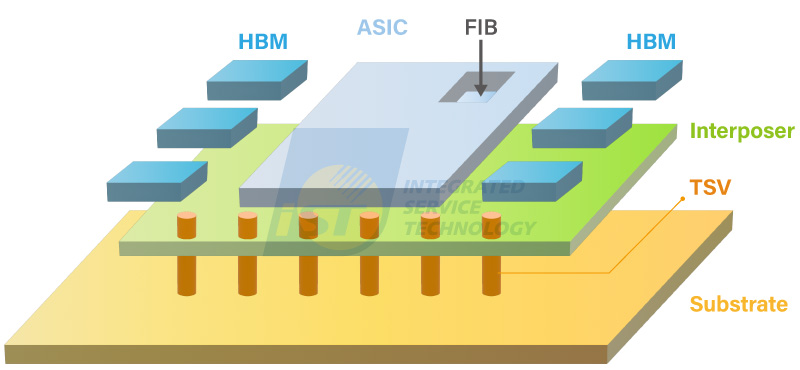

3. CoWoS(Chip-on-Wafer-on-Substrate)

近两年,CoWoS封装无疑是最受关注的封装技术之一,那么,这种封装能否进行FIB电路修补呢?答案是肯定的!

从结构示意图中可以看到,CoWoS采用了2.5D封装形式,AS芯片的正面透过TSV(Through-Sil芯片on Via)连接到基板(Substrate),而AS芯片芯片的晶背则为裸露状态,所以可以从晶背进行FIB电路修补。

然而,在进行FIB修改之前,通常需要先对晶背进行研磨以减少其厚度。传统上,研磨通常是全面性进行,但这样容易破坏高带宽内存(HBM)。宜特可以针对FIB的目标区域进行局部研磨,这样不仅能保护HBM,还能为后续的FIB操作提供必要的空间。

宜特科技是台湾首家执行FIB电路修补的民营实验室,30年来的电路修补经验,成功解决了无数客户的各种挑战,从简单的1L1C电路修补到复杂的电路问题;或是从单站的FIB电路修补,到跨越3~4站的故障分析(FA),都能提供对应的解决方案。

2018年,宜特率先提供7nm工艺芯片背电路修补服务;2021年初,成功展示了5nm工艺的芯片背电路修补技术。2023年底,宜特更成功完成了3nm芯片电路修补案例,帮助客户迅速确认电路缺陷,降低开发时间与成本,加速产品上市。

宜特FIB电路修补,不仅在各工艺节点的技术演进中,始终保持领先地位,成为众多芯片设计公司首选的合作伙伴之外,后续更可结合宜特一站式的故障分析和材料分析解决方案,搭配30年丰富的大数据经验,将如虎添翼协助芯片设计业者解决棘手的芯片除错问题。本文与各位长久以来支持宜特的您,分享经验,若您想要更进一步了解细节,欢迎洽询+886-3-5799909 分机6000 王先生│Email: web_fib@istgroup.com。