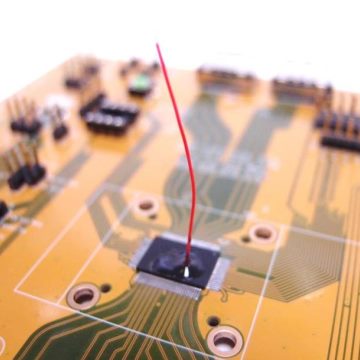

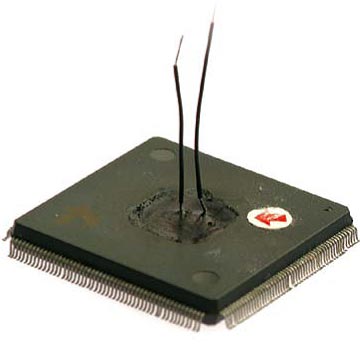

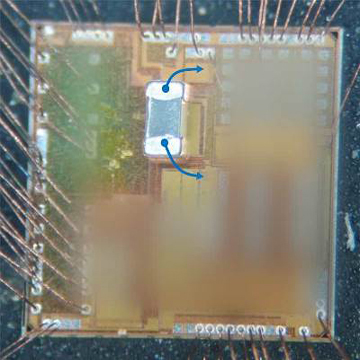

在芯片表面使用聚焦离子束形成导电孔及导电垫子,再利用特殊接合方式使导电垫子连接金属导线,以形成导电路径。

iST 宜特服务优势

| 优势比较 | N-FIB | 传统 FIB |

|---|---|---|

| R esistance with long wiring (1000 μ m) | 1 Ω± 10% | 7000 Ω± 10% |

| Parasitic capacitance | < 200fF | Less |

| Parasitic inductance | ~0.5nH/mm | Less |

| Current limit | Less | Possible |

| Power line | 1A | 3mA |

| Insert device | Yes | No |