发布日期:2020/12/15晶圆减薄

发布单位:iST宜特

功率半导体的轻薄短小,是现今热门议题与未来趋势.

但随着芯片减薄后,接踵而来的风险是什么 ?

要如何有效地来抑制并降低工艺上的风险呢 ?

Wafer Ultra Thinning

功率半导体进行「减薄」,一直都是改善工艺,使得功率组件实现「低功耗、低输入阻抗」最直接有效的方式。晶圆减薄除了有效减少后续封装材料体积外,还可因降低RDS(on)(导通阻抗)进而减少热能累积效应,以增加芯片的使用寿命。

但如何在减薄工艺中降低晶圆厚度,又同时兼顾晶圆强度,避免破片率居高不下之风险,则是各家晶圆后端工艺厂所钻研的技术重点。

晶圆减薄

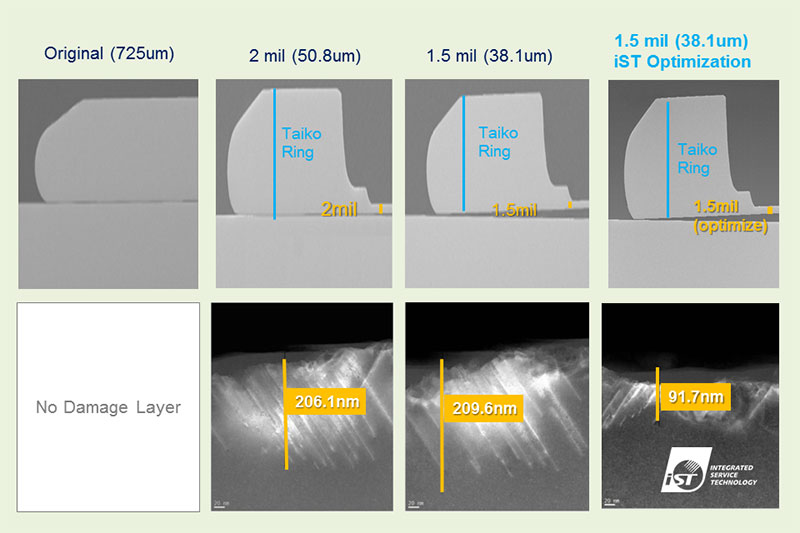

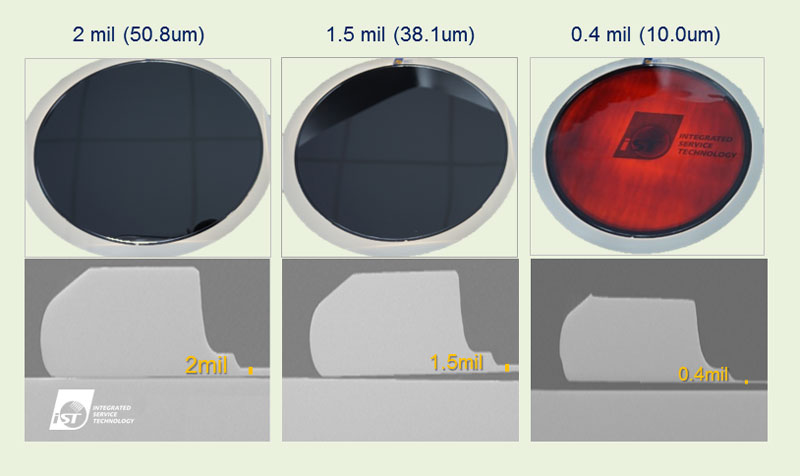

为解决此风险,iST宜特目前已完成2mil(50um)、1.5mil(38um),甚至到0.4mil(10um) 减薄技术开发,特别是0.4mil的薄如蝉翼的晶圆(参见图一),在背面白光光源照射下,晶圆表面有如婴儿肌肤般地透出红光。

图一:2mil、1.5 mil、0.4mil晶圆减薄,透过扫描式电子显微镜 (SEM)情形

本期iST宜特小学堂,也将与您一同分享晶圆减薄(降低晶圆厚度)后,如何提升晶圆强度。

一、从芯片研磨探讨

一片8吋晶圆裸片原始厚度为28.5 mil(725 um),在经过减薄后,可将厚度降低至2mil (50um)、1.5mil (38um)、甚至0.4mil(10um)。

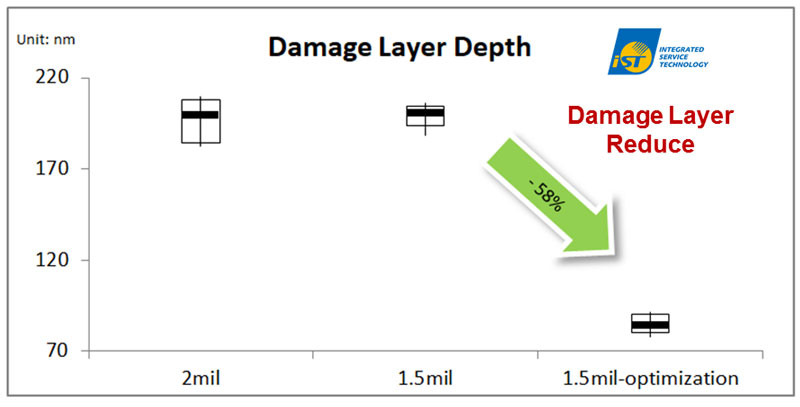

不过减薄难免会产生损伤,藉由穿透式电子显微镜 (TEM)分析芯片表面损伤程度可发现,随着研磨量增加,表面损伤层(Damage layer)深度随之增加(图二),进而造成机械应力累积,使得芯片强度降低,因此造成后续封装测试工艺的难度。

iST宜特可藉由特殊的优化工艺来改善此一现象以提高生产良率(图二)。

图二:使用控片测得2mil、1.5 mil、1.5 mil优化条件后的损坏层厚度及TEM分析

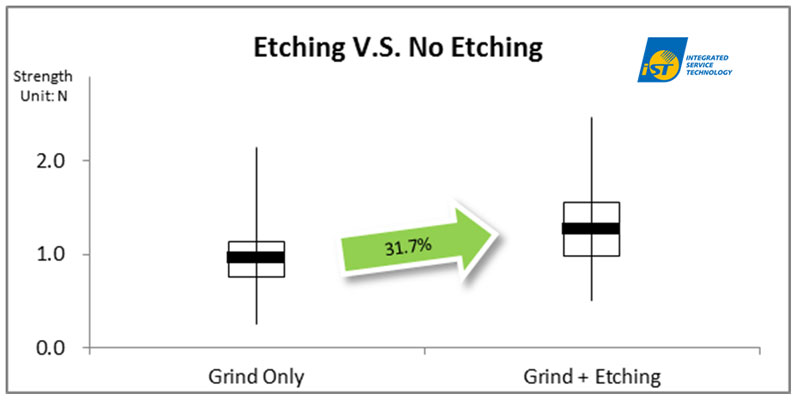

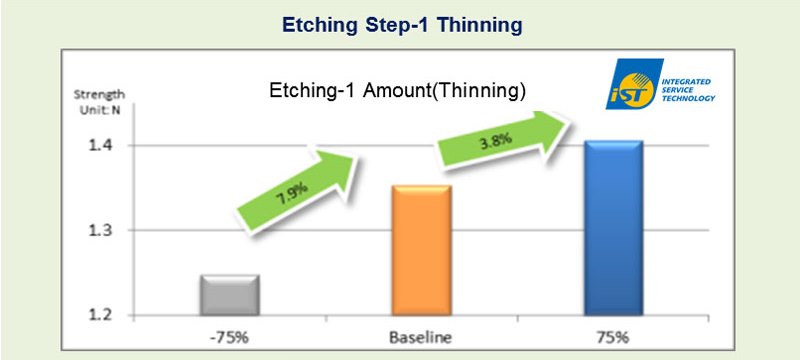

二、从晶圆蚀刻来探讨Die Strength的提升

以上与您分享宜特的相关技术,若您有相关需求,iST宜特可以配合您进行后续的工程开发,为您提供Power MOSFET/IGBT等组件的減薄强度改善,欢迎洽+886-3-579-9909分机5888 游先生(Stan) │ web_sp@istgroup.com