发布日期:2022/4/12SiP失效

发布单位:iST宜特

MCM/SiP等复杂多芯片结构,如何针对疑似失效

芯片进行确认?

如何避开其他组件的干扰,正确判定测试结果?

随着多媒体影音/高速通讯组件等科技产品,朝向多功能化与IC体积微小化迈进,组件间的系统化整合也被视为未来的重点发展技术。目前业界的封装技术大多朝SiP (System in Package;系统级构装)、MCM (Multi Chip Module;多芯片模块) 进行优化。

然而,当IC出现失效时,想分析其中一颗组件或晶粒(Die)的异常状况,又碍于SiP、MCM内部打线或基板线路互相联结的复杂关系,将导致进行电性测试时,容易受到其他芯片或组件影响,造成判定困难,甚至无法判定。

该如何解决此状况呢?本期宜特小学堂,将与您分享解决之道。宜特藉由累积多年厚实的半导体验证分析技术,研发出IC Repackage移植技术,可从SiP、MCM等多芯片或模块封装体里头,将欲受测之裸Die,无损伤的移植至独立的封装测试体,避开其他组件的干扰,进行后续各项电性测试,快速找到IC失效的元凶是谁。

SiP失效

一、IC Repackage 移植五步骤

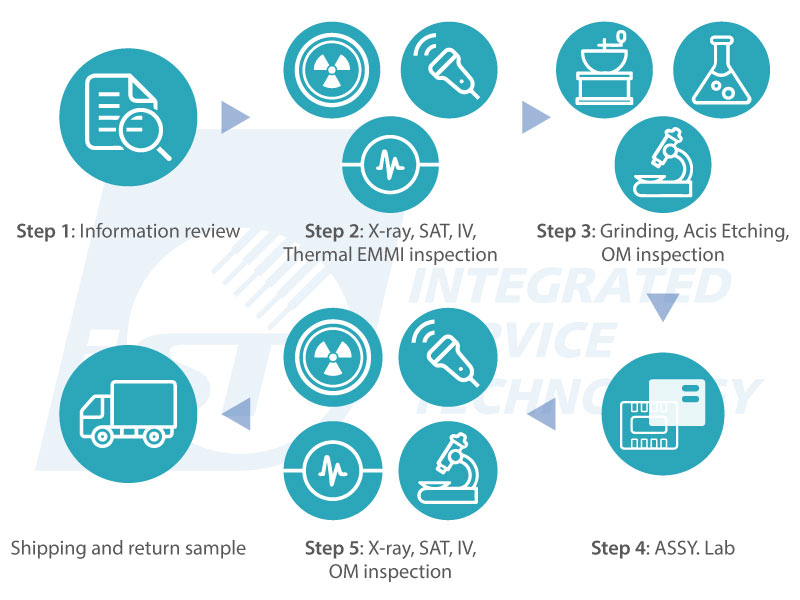

进行IC Repackage 移植,在宜特实验室需要经过五道步骤(图一)。

首先,收到待测样品后,宜特将进行IQC(Incoming Quality Control,样品进料质量控制),并确认客户提供的相关信息,包括利用3D OM检查外观有无受损、确认封装体内Die的数量、目标异常芯片位置与厚度等,这个阶段主要目的是确认样品现况是否吻合客户反应情形。

第二步骤,将利用X-ray(X射线检测)或SAT(超音波扫瞄),进一步确认目前样品有无封装(Package) 异常,并定位确认需要取出的目标异常芯片位置。 接着,藉由IV电特性量测,来确认封装体内,客户指定pin的状况,同时,视情况,将利用Thermal EMMI (InSb) 来确认亮点与目标异常芯片的关系。

第三步骤,则是利用酸蚀及研磨方式,取出目标异常芯片,并藉由OM(数位显微镜),确认芯片有无Crack(裂痕)、Burnout(烧毁)、Chipping(缺口)等问题。

第四步骤,将取出的裸Die,重新打线封装成客户要求的Package。最后,宜特可先针对样品进行IV电特性量测,或是,客户也携回该颗重新封装过后的IC,至自家厂内进行功能性电特性量测。

图一:宜特科技实验室 IC Repackage移植五步骤

二、IC Repackage 移植经典案例

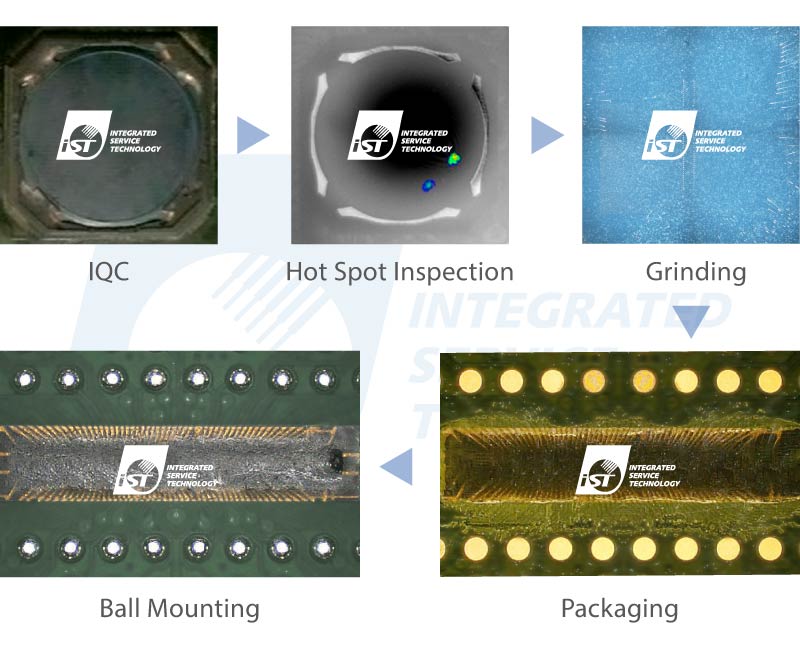

■ 取出SiP中的目标异常Die,制备成wBGA

图二为SiP样品,宜特科技透过Repackage移植技术,将其中的目标异常裸Die取出,进行样品制备,移植成wBGA (window Ball Grid Array) 封装形式。藉此,客户即可避开其他组件的干扰,针对该颗wBGA进行后续ATE(Automatic Test Equipment),确认异常位置。

图二:移植SIP里头的目标裸Die,样品制备为wBGA封装形式,顺利进行后续各项测试。

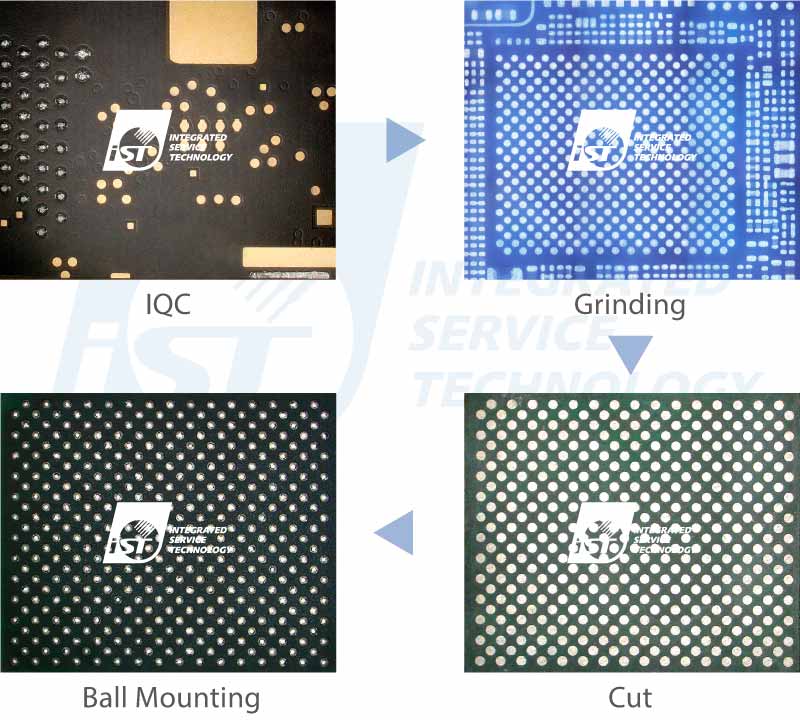

■ 从Module(模块)中取出组件,进行植球

当Module (模块)中有多颗IC或组件时,宜特实验室透过研磨或切割,将目标组件从Module中取出,接着进行植球服务,让客户可以取回至自家厂内进行各项测试,厘清相关故障原因。

下图为从Module(模块)中取出我们的目标BGA IC,经过尺寸量测及植球后,便于客户后续测试。

图三:取出Module内的目标组件,经植球后,即可回到客户厂内测试。

本文与各位长久以来支持宜特的您,分享经验,若您有关于IC Repackage相关知识或需求想要更进一步了解,欢迎洽询+886-3-579-9909 分机6755欧先生│Email: IST_FA_IAD@istgroup.com / marketing_tw@istgroup.com