发布日期:2022/8/2材料接合应力强度

发布单位:iST宜特

不同种类的材料封装在一起,衍生挑战接踵而至,

如何确保异质整合组件的可靠性? 如何量测材料间的附着能力与结合强度?

随着5G、AI等新兴科技应用兴起,半导体制程持续微缩,对封装的要求也愈来愈高,具备高度芯片整合能力的「异质整合」封装技术,被视为后摩尔时代下延续半导体产业发展的动能。所谓「异质整合」为将两个、甚至多个不同性质的主动与被动电子组件,整合进系统级封装中 (System in a package, SiP)。

然而,欲将不同种类的材料封装在一起,衍生的挑战亦接踵而至。举例而言,在覆晶封装 (Flip Chip Package,FCP)中,底部填充剂 (Underfill)的选择就会影响异质整合组件的可靠性,在宜特可靠性验证分析实验室里,常见异质整合组件的故障模式,包括填料沉降 (filler settling)、空隙 (void)与翘曲(Warpage)产生,因此,若能掌握Underfill的流变特性,对于制程优化有所帮助)。

另一方面,在异质整合先进封装技术中,表面的机械特性与异质材料间界面的附着能力,将影响组件可靠性。本期宜特小学堂与安东帕公司合作,将介绍如何藉由分析工具,确认异质整合组件材料中Underfill的流变特性,以及金属铜、介电材料等的接合应力强度。

材料接合应力强度

一、 如何量测Underfill材料流变特性: 动态剪切流变仪

材料的流变特性,主要用来描述材料受到应力后产生流动或形变行为,对于「流体」而言,常用「黏度」来表示流体受力后流动的难易程度;而对于「黏弹体」则使用「储存模数 (Storage module) 」以及「耗散模数 (Loss module) 」表示。可透过动态剪切流变仪来进行试验。

利用材料放置于一几何形状皆被定义好的系统中(例如: 锥板量测系统、同心圆柱量测系统),藉由精密的马达控制系统,给予材料一默认的剪切应力,量测材料所相应产生的剪切应变,可得到材料的相关流变特性包含储存模数、耗散模数、或者阻尼因子。除此之外,由于流变仪可搭载不同的控温系统,除了了解材料的本质特性以外,亦可用来模拟材料于制程中受力下的流变行为变化。

在FCP制程中,Underfill是用来填充芯片与基材中间的空隙,其通常是由环氧树脂 (Epoxy)作为基材并添加硅粒子降低填充剂的热膨胀系数。首先将 Epoxy涂抹在芯片的边缘,再透过毛细作用让材料自动渗透到覆晶芯片的底部,之后再加热予以固化。

为了降低制程时间及增加生产力,新一代的Underfill黏度越做越小,然而此方法对于添加物的悬浮稳定造成负面的影响,添加物于黏度较低的材料中易于沉降。因此,如何克服添加物沉降 (filler settling)以及减少空隙 (void)的出现为一重要的议题。

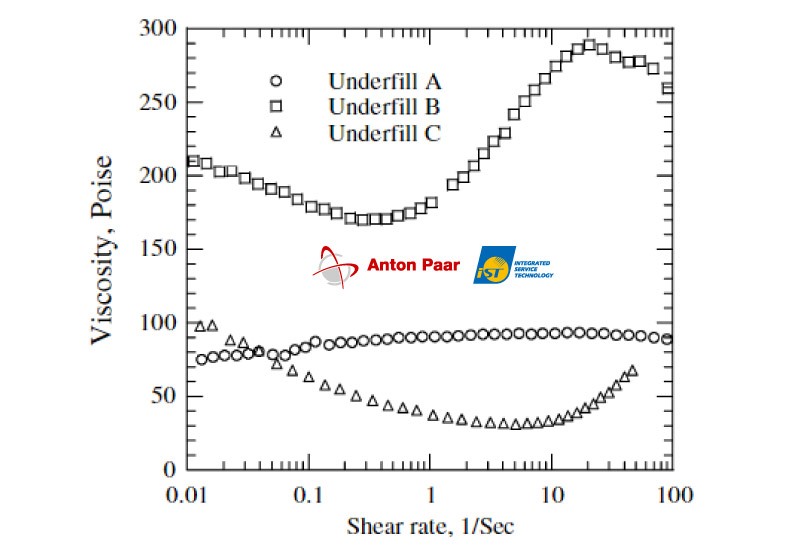

以下为利用流变仪,探讨三种不同的底部填充剂( Underfill A, Underfill B, 以及 Underfill C)的流动特性,图一为此三种材料的黏度曲线,由结果可发现此三种填充剂的流变特性非常不同,Underfill A为「牛顿流体」、Underfill B和Underfill C则于高剪切力下呈现「剪切增稠」行为。除此之外,三款Underfill皆具有一「降伏应力(Yield Stress) 」。

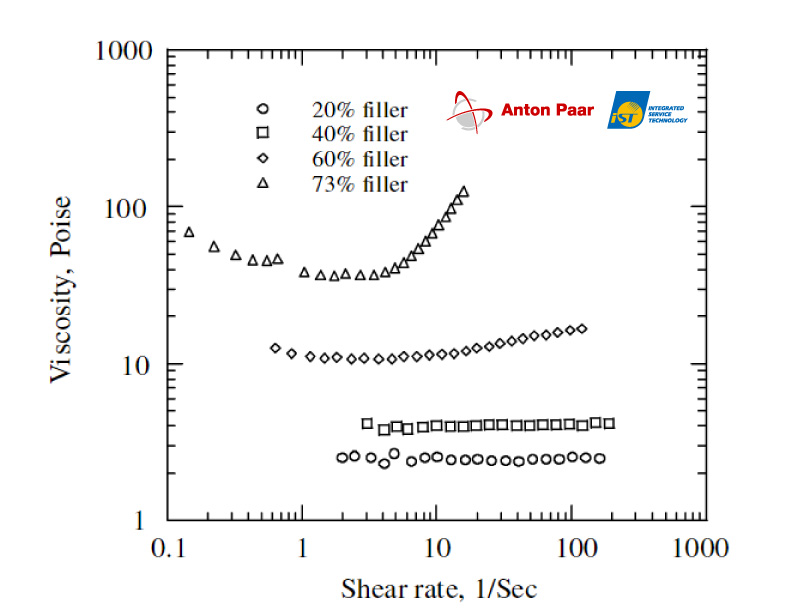

综合实验结果可发现,Underfill中添加剂的含量多寡对填充剂的流变行为有非常显著的影响,如图二所示,在添加物含量在40%以下时,Underfill呈现「牛顿流体」的流动行为;当添加物含量大于60%后,Underfill的黏度会随着剪切力的改变而改变;当添加物含量高于73%以上后,在剪切速率大于5 1/s后,黏度会随着剪切率的上升而上升,呈现剪切增稠的流变行为。此外,具有降伏应力以及快速的流动特性的Underfill能降低填充剂沉降发生的机率。

二、 如何量测异质整合材料间的附着能力与结合强度-压/刮痕测试仪

异质整合技术涉及到将具有不同特性的材料整合在一起,因而材料与材料之间的附着能力以及结合强度为影响组件可靠性的重要因子之一。

压痕测试技术为一可精准测量出薄膜、涂层以及块材的机械特性方法,不论是软质(Soft)、硬质 (Hard)、具脆性 (Brittle)亦或具延展性(ductile)的材料,其力学特性包含硬度 (Hardness)、弹性模数 (Elastic modulus)、弹性和塑性功 (Elastic and plastic work)或是蠕变 (Creep)特性等皆可得到。

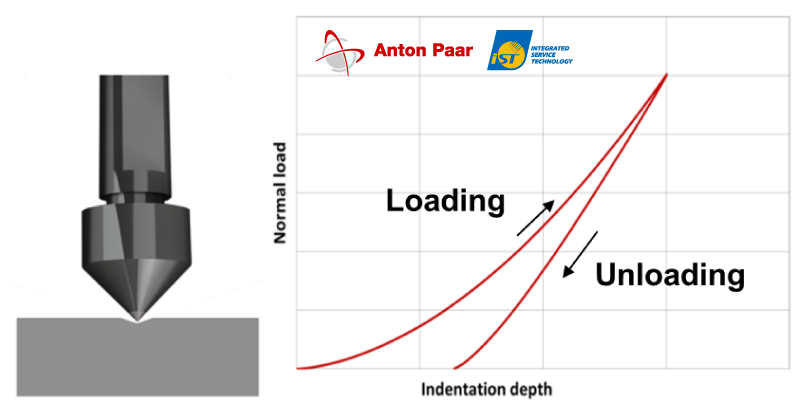

传统的压痕测试方法为透过一已知几何形状的压头 (indenter),于材料表面上施加预设载荷 (Load)压入材料,并藉由测量压痕塑性变形面积得到材料的硬度。然而,在微米及奈米的尺度下,由于产生的压痕很小,不易准确地测得压痕面积,用传统的测试方法无法得到微米/奈米材料的硬度。

因此,微米/奈米压痕测试仪具有精密的应力和深度传感器,可精准地控制压头进行加载与卸除的过程,并于过程中同时记录载荷及压入深度。透过图三所示之「连续荷载-压深曲线」并通过理论模型,可计算出材料的力学特性。

此外,若要量测涂层的附着力和结合强度与抗刮能力,刮痕测试仪为一公认的涂层材料测试方式。

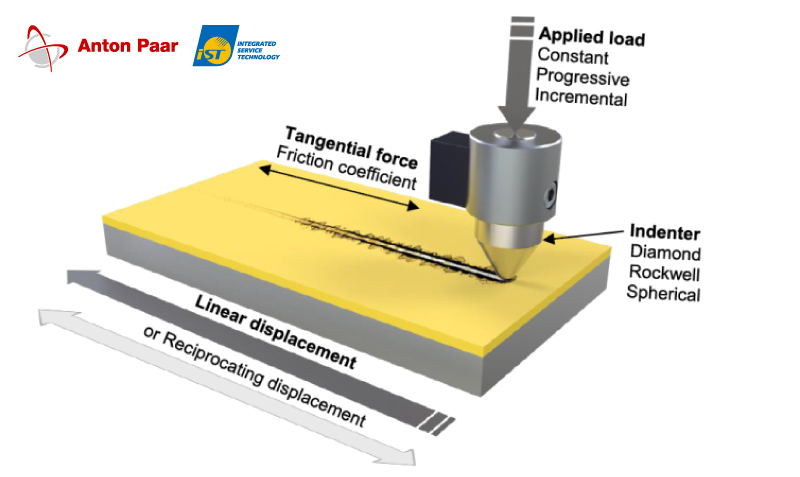

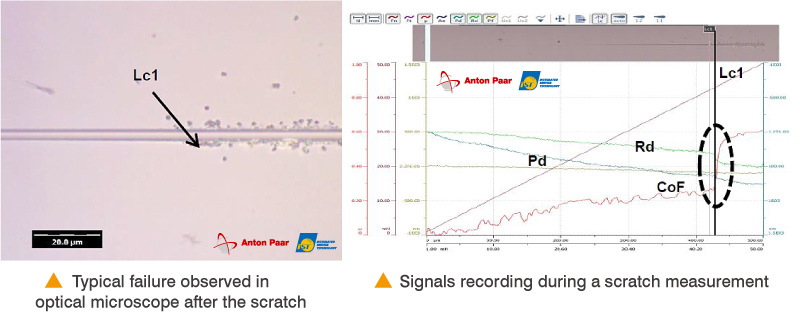

利用一已知形狀的鑽石壓頭壓在待測表面上,當待測樣品以預設的速度移動時,壓頭會於待測表面留下刮痕(如圖四所示)。於下壓過程中,若施加在壓頭的載荷為一恆定值,可測試材料刮痕硬度或是抗刮能力;若施加在壓頭的載荷逐漸增加,並於此過程中同時記錄正向作用力與磨擦力、下壓深度以及聲波訊號的變化,則可用來了解材料的附著能力。

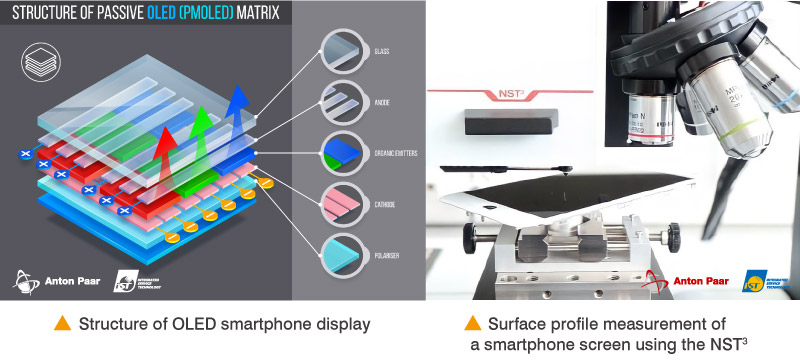

利用刮痕测试仪来研究异质材料间的附着能力已广泛地被应用在汽车以及显示面板产业中,举例而言,图五为利用刮痕测试仪,测试智能型手机面板玻璃的抗刮能力,此玻璃表面具有厚度约为 100 奈米 (nm)的氧化铝保护层,实验中采用半径为2微米 (μm) 的球锥形状 (Sphero-conical)刮头,刮头的最大载荷力量为50 毫牛顿 (mN)。

图五:手机面板表面100 nm厚的氧化铝护层之刮痕测试

(Ref: Anton Paar application report: Mechanical surface characterization of smartphone displays)图六(左)为于玻璃表面创造出的刮痕及其失效模式,图六(右)为正向作用力与下压深度 (Pd)、残留深度 (Rd)以及磨擦系数 (CoF)的变化,在临界载荷位置(大约44毫牛顿),可观察到涂层失效行为,与此同时,可观察到下压深度、残留深度以及磨擦系数亦有显著的变化。若要得到具有良好附能力的涂层,临界载荷位置越大越好。

三、 如何计算3D封装硅通孔(TSV)中铜的力学特性

3D封装为达成异质整合重要的技术,于3D封装技术中,硅通孔(Through Silicon Via, TSV)为实现芯片垂直整合的主要技术,制作完成的TSV结构具有许多的金属界面,在硅通孔中铜金属的扩散作用以及铜晶粒的大小对于铜的力学特性有很大的影响。因此,若能正确的建立硅通孔中铜的力学特性,对于TSV结构的可靠性分析和设计有显著的帮助。

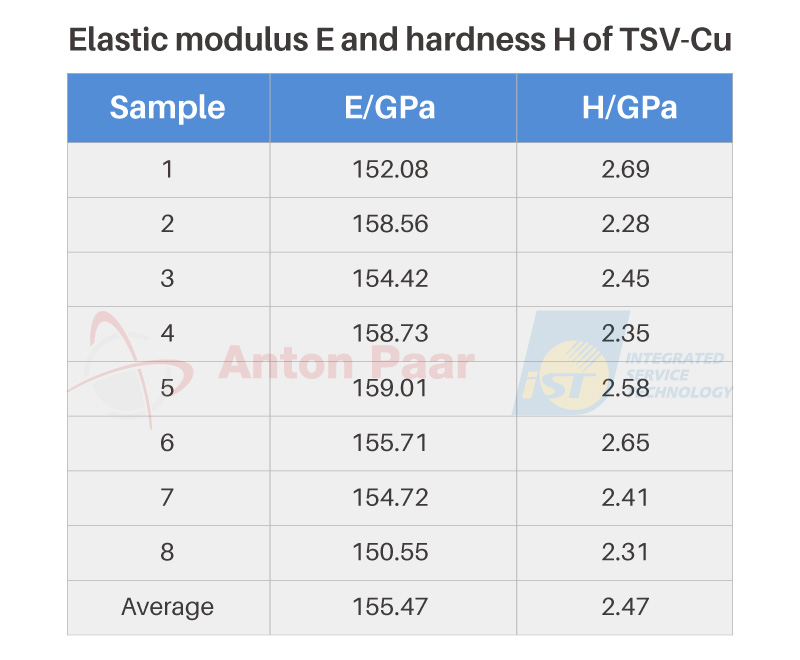

为了求得TSV-铜的弹性模量,使用奈米压痕测试仪搭配Berkovich压头,在TSV-铜外露表面靠近圆心位置进行奈米压痕实验,压入深度为500奈米。所得到材料的弹性模量以及硬度,为下表所示:

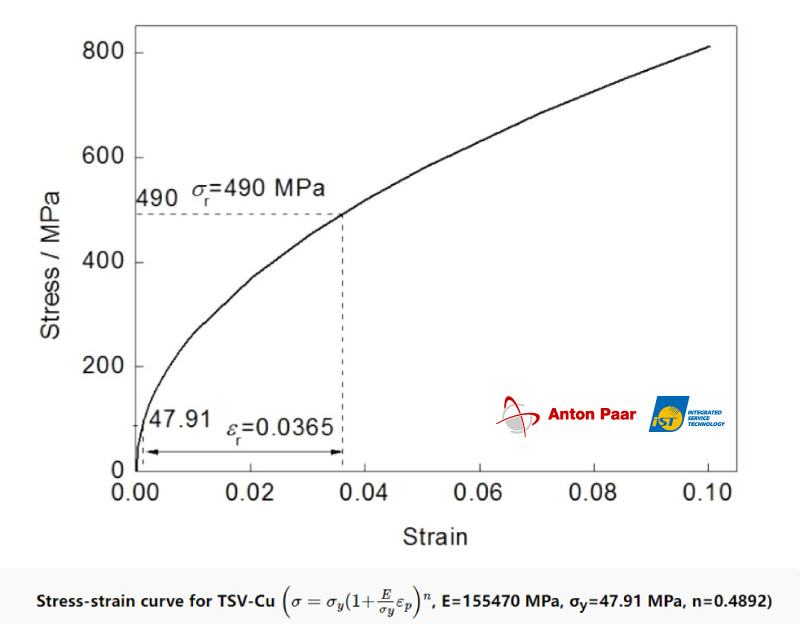

有了此结果并搭配有限元素分析方法可进一步地推算出材料的应力-应变曲线,如图七所示计算出TSV-Cu的弹性模量、应变强度指数与降伏强度分别为155.47 GPa, 0.4892和47.91 MPa。

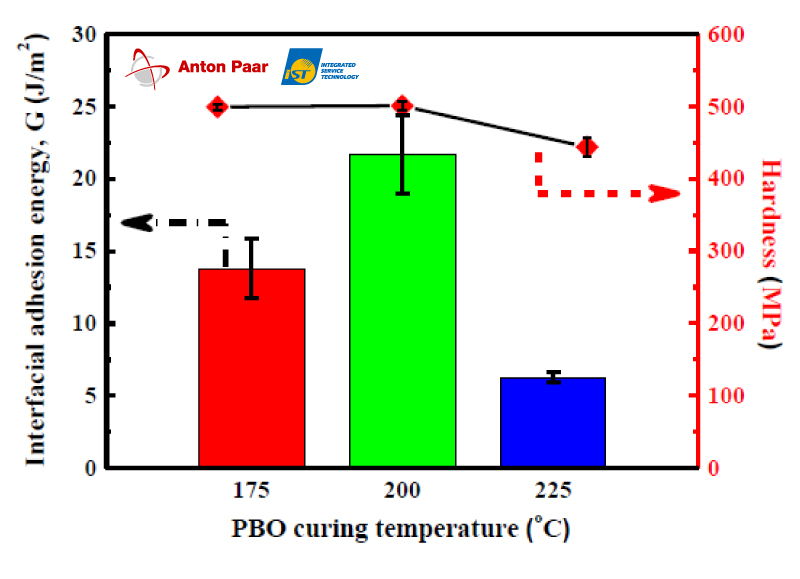

四、 如何测试介电材料(PBO)固化温度对于表面硬度之影响

扇出型晶圆级封装 (Fan-Out wafer level package,FOWLP)为新颖性封装技术,于此制程中,重分布层 (redistribution layer, RDL)的制备为一关键步骤。而于FOWLP中,其RDL一般由介电材料(如PI、PBO)与铜(Cu)所组成,若要得到具有可靠性良好的产品,介电材料与铜之间需有很强的附着能力,以能承受可靠性测试中高温高湿的考验。因此,在此实例中,可利用奈米压痕测试仪了解不同的固化温度对于材料硬度的影响,此实验搭配Berkovich压头,控制最大压深深度为 500奈米,针对不同固化温度的PBO进行分析。实验结果显示PBO的硬度随着固化温度上升先是持平后,到225度而开始下降(如图八所示)。除了了解PBO机械特性以外,未来亦可搭配刮痕测试仪进一步地量测出RDL铜与介电材料的附着能力,进而将制程优化。

在先进异质整合封装的产品技术开发阶段,除了前述的材料分析技术之外,宜特科技实验室也有提供相关Underfill 改善Void发生的制程技术,以及采用四点探针弯曲测试金属与介电材料间附着力的多年经验,不但能辅助提供材料的机械性质外,还可搭配相关的热性质、可靠性、寿命测试等,以完成产品的所有验证。一旦经过高温、高湿、或震动测试后才导致故障失效,就需要找出并探究产品故障的因子,作为材料微调或制程改善的依据。因此,如果想要缩短产品开发的时程,节省设备成本的耗费,宜特科技具有全方位完整的解决方案,能够提供以上各种相关材料分析、可靠性验证、故障分析的服务,以满足客户所要的规格与需求。

本文与各位长久以来支持宜特的您分享,若您有相关需求,或是对相关知识想要更进一步了解细节,欢迎洽询 +886-3-579-9909 分机 6613 张先生 / Email: SA_TW@istgroup.com ; marketing_tw@istgroup.com。

参考文献:

- 纳米压痕法确定TSV-Cu的应力-应变关系;秦飞,项敏,武伟;北京工业大学机械工程与应用电子技术学院, 北京100124, 2014 《金属学报》 50 (6): 722-726 https://www.ams.org.cn/article/2014/0412-1961/0412-1961-50-722.shtm

- Effect of dielectric process on the interfacial adhesion of RDL for FOWLP, 2377-5726/20/$31.00 ©2020 IEEE

- Mechanical surface characterization of smartphone displays, Anton Paar XCSIA086EN-A.

- The effects of rheological and wetting properties on underfill filler settling and flow voids in flip chip packages, Microelectronics Reliability 47(12):1958-1966.

本文作者:

安东帕公司、宜特科技股份有限公司

本文同步刊登于:

电子工程专辑 2022年8月号《封面故事》