随芯片朝轻薄短小发展,在更小的晶粒中有更多的I/O数量,且晶粒体积不断微型化,使得终端产品电磁干扰(EMI)的情形更加恶化,电磁耐受的能力(EMS)大幅降低。

然而由芯片所诱发的电磁兼容(EMC=EMI+EMS),若到产品设计后段(终端产品)才正视,将更难解决。因此在芯片设计时间,就应了解芯片 EMC状态,并对芯片实施电磁干扰防治措施,将可大幅降低电磁干扰产生的机率与产品修改成本。

iST宜特服务优势

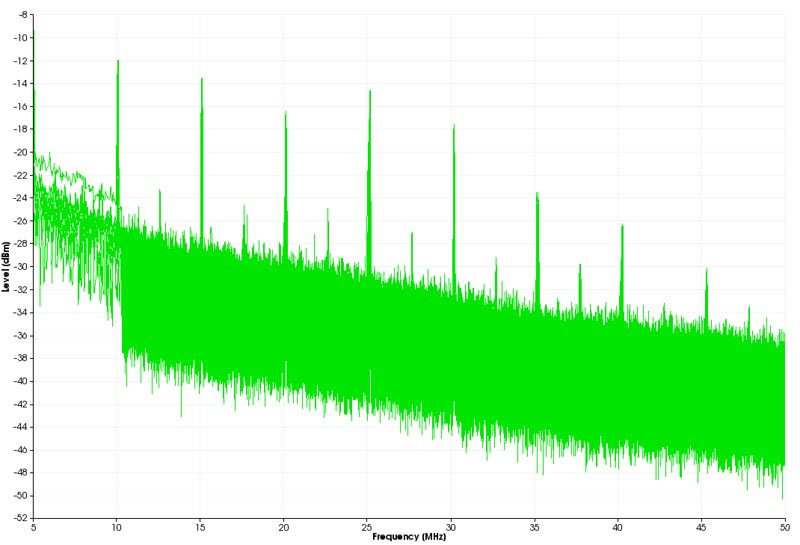

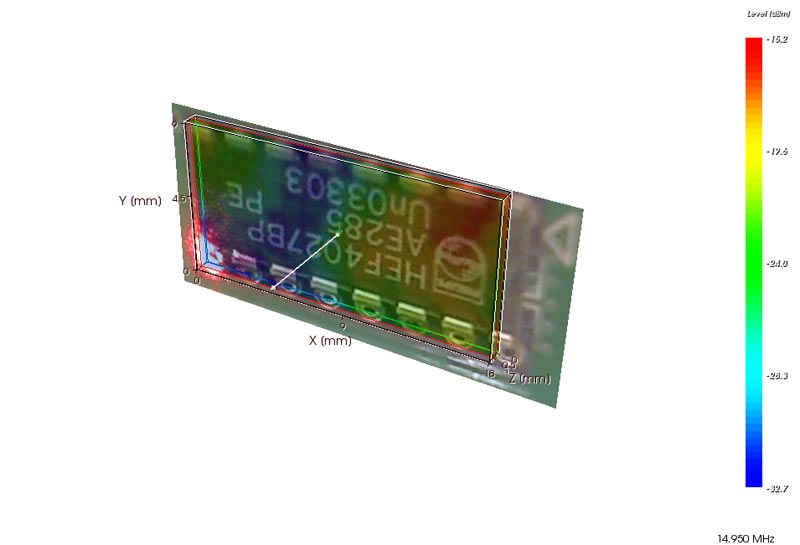

从芯片 EMl电路板Layout/制作,到芯片 EMI量测/分析,均能够提供完整测试服务,并依照规范出具试验结果比对报告。

参考规范

TEM Cell横向电波室测试

- SAE-J1752/3(美国汽车工程师协会制定)

- IEC 61967/2(国际电工委员会)

- AEC-Q100(美国汽车电子协会)

Near Field Scanner近场扫描量测

- SAE-J1752/2

- IEC 61967/3