发布日期:2017/8/17

发布单位:iST宜特

计算机仿真组件上板应力匹配正常,可靠性实测却过不了,是组件与板材匹配问题?还是封装锡球的耐受度不够?

组件重新跨制程,经过可靠性验证,实验结果却显示高阻值异常失效点该如何找?

本月的小学堂,宜特将分享一个以晶圆级芯片尺寸封装(WLCSP)的组件,进行上板可靠性验证后,产生失效的案例。此案例对于以锡球为封装形式的IC,亦是相当常见的失效形式。

所谓的WLCSP晶圆级芯片尺寸封装,全名Wafer Level Chip Scale Packaging,是指,直接将整片晶圆级封装制程完后,再进行切割,切完后封装体的尺寸等于原来晶粒的大小,后续利用重分布层(RDL),可直接将I/O拉出数组锡球与PCB做连接。

也因随着轻薄短小的需求,WLCSP成为封装形式的主流,在WLCSP的封装体概念下衍生出Fan-in,Fan-out与Info等晶圆级封装体。然而,此类封装形式,在可靠性验证后,常见的失效模式,如锡球接口、吃锡不良,上板后应力匹配问题。

所以,当要确认WLCSP形式的组件,在可靠性验证后的失效点时,就更需要留意分析工具的时机点是否会有应力产生,免得反而破坏掉「命案现场」(原有的失效点),导致更难确认失效真因。

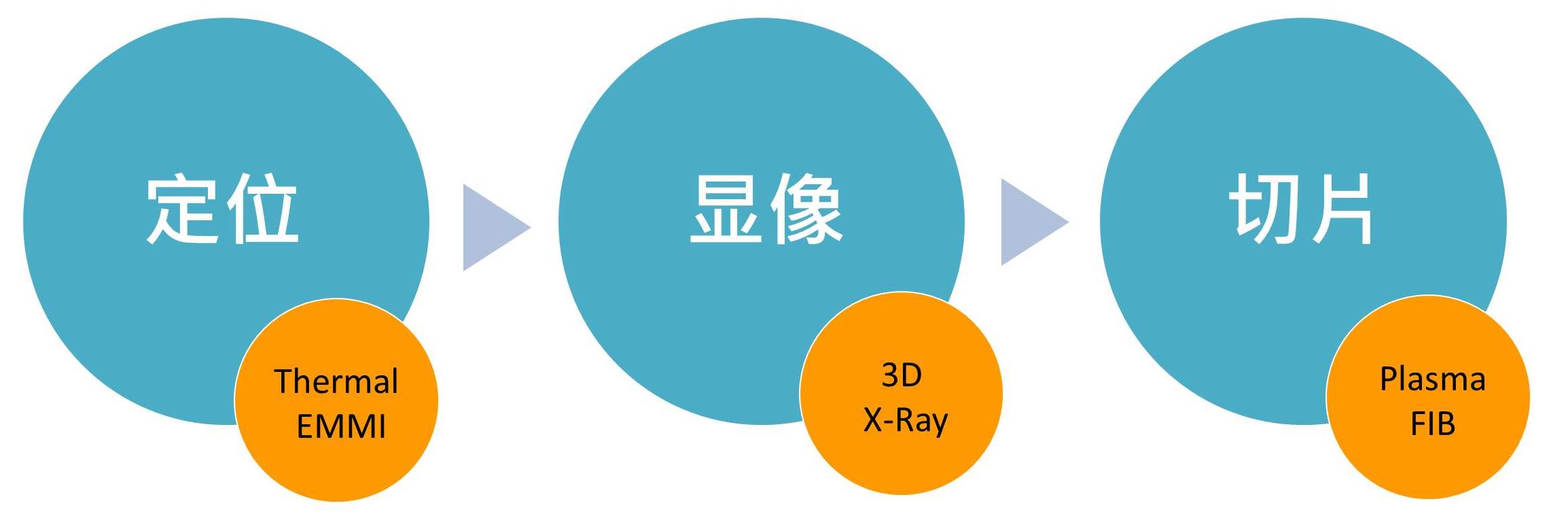

以下这个案例,宜特提出三步骤,告诉你失效分析工具该如何选择?特别是什么时机点,命案现场才能够清除,快速让失效点(defect)无所遁形。轻易找到失效真因。

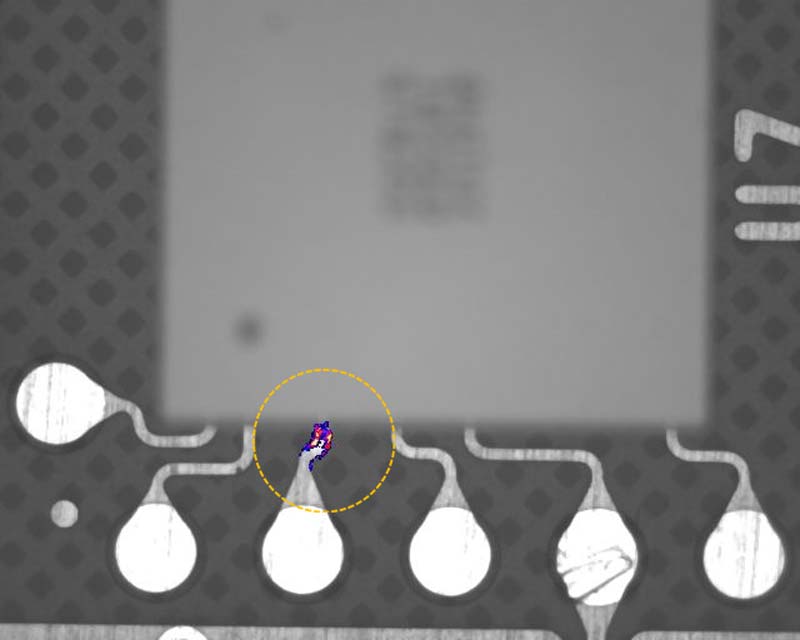

第一步骤 : 定位

针对可靠性实验后产生高阻的WLCSP组件,利用Thermal EMMI故障点热辐射传导的相位差,定位到失效位置,是在Solder Ball 地方。

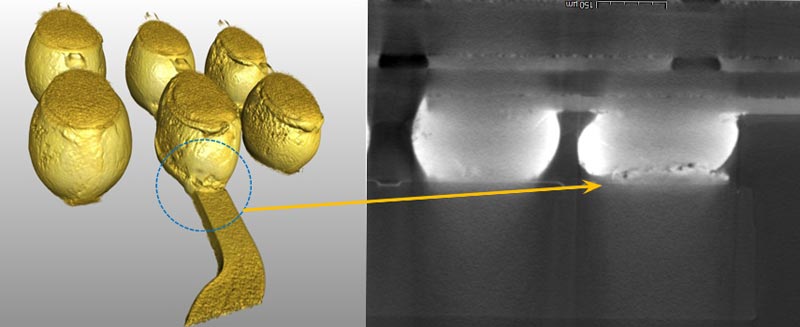

第二步骤 : 显像

接着,为了不破坏「命案现场」,因此使用3D X-ray进行立体图(左下图)与断面图(右下图)显像,找到原来是锡球(Solder Ball)有损毁状况。

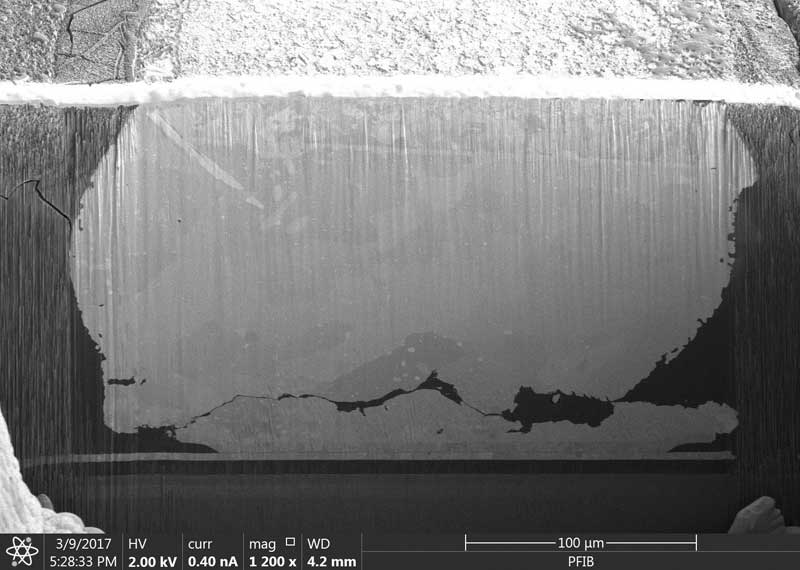

第三步骤 : 切片

在已确认Defect相对位置时,此时即可移除「命案现场」,使用低应力Plasma FIB工具,将失效断面切出并分析真因,找到原来是Solder Ball Crack状况,导致组件高阻值异常而失效。

本文与各位长久以来支持宜特的您,分享经验,若您有可靠性验证后,组件异常状况不知如何分析,或是对相关知识想要更进一步了解细节,欢迎洽询中国免费咨询电话: 400-928-9287│ Email: marketing_chn@istgroup.com ; 或洽询+886-3-579-9909 分机8595 陈小姐│Email: ist_fa_iad_icfaiii@istgroup.com。