发布日期:2019/3/14

发布单位:iST宜特

随着工艺越微缩,越小工艺的芯片,该如何成功完成FIB电路修补?

随着摩尔定律,半导体工艺从1微米(um)、0.5微米(um)、0.13微米(um)不断微缩到奈米(nm)等级,如此先进工艺的电路修补,考验FIB实验室的技术发展及应用能力。特别当工艺来到16奈米(nm)以下的工艺,包装型式多数为覆晶技术(Flip Chip),因此FIB电路修补就必须从芯片背面(简称晶背,Backside)来执行,整体困难度也随之增加。

2018年,宜特IC FIB电路修补实验室,就陆续收到7奈米(nm)工艺,必须从晶背进行电路修补的样品。据了解,此样品难度之高,令其他同业望IC兴叹、束手无策。宜特早年是从IC FIB电路修补起家,2015年时完成20/16奈米(nm)芯片正面的电路修补技术,并于2016年挑战完成16奈米的IC 晶背(Backside)FIB电路修补技术(参见图一)。近期宜特接到7奈米(nm)的案子,藉由多年经验,成功完成此电路修补。

本次小学堂,将与各位聊聊,先进工艺等级及 7奈米IC晶背电路修补的难度,以及宜特如何克服完成它。

一、 7奈米线路微缩倍增,难度大提升

能够让您的IC样品在FIB电路修补后,可以回去做电性测试,是不论怎么样的工艺都必须要的基础条件。有了这个前提下,宜特工程师将会和您讨论三大要点:1. 了解您设计的IC电路特性与修补目的

2.建议电路布局及讨论可破坏范围 3.精准协助您寻找最佳目标点,提高电路修补可行性。

而当随着芯片晶体管的密度随着工艺微缩而倍增,今年7奈米每平方毫米的密度约为16nm的3.5倍,难度肯定大幅度上升。不过不管什么工艺,以上三大要点是FIB电路修补前需讨论沟通的基础工,忽略不得。二、 晶背修补两大关键技术- 前置处理Substrate层的厚度与End Point的停留位置

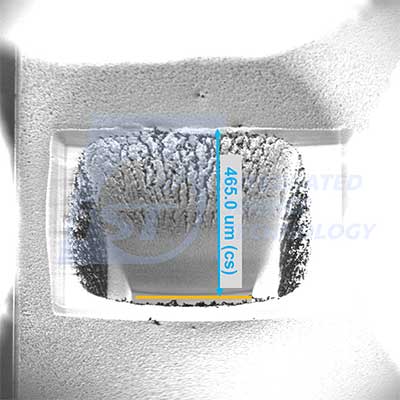

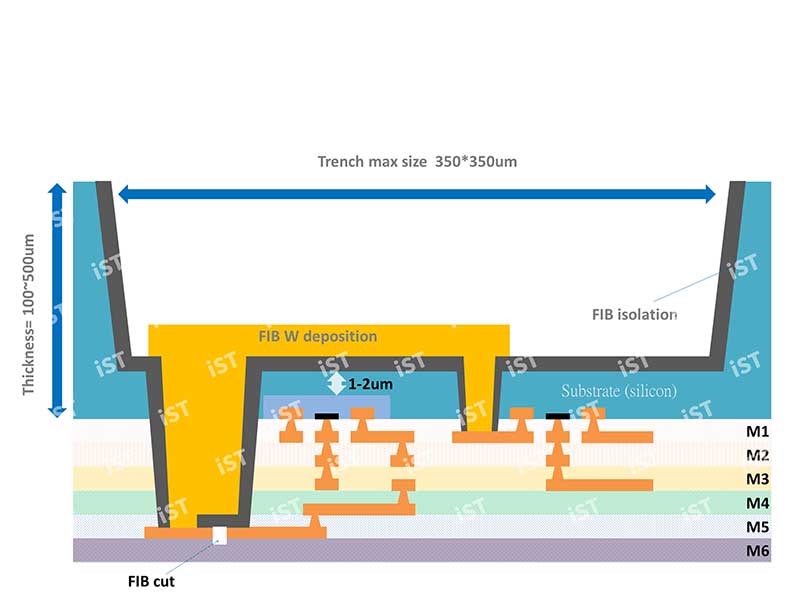

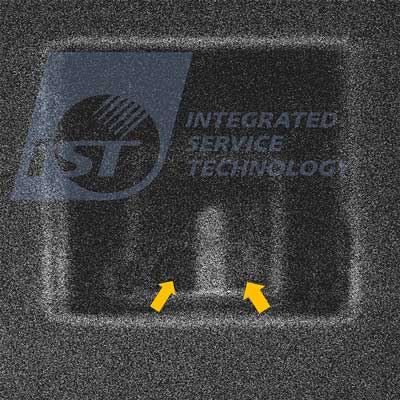

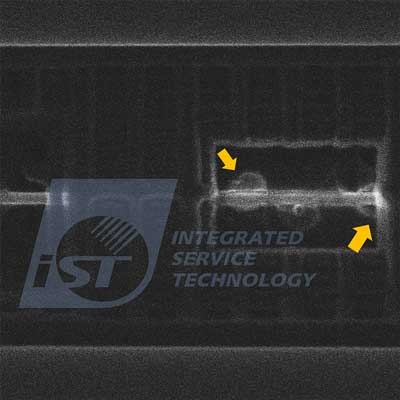

进入晶背(Backside)修补工程的第一个阶段,首先面对的是Substrate层(Silicon);终端产品形式会决定包装厚度规格,其芯片的厚度,通常由硅晶圆时的31mil,研磨至8~12mil,不过这样的厚度,对微/奈米等级的FIB电路修补并无法直接开始手术,为此,我们将依照第一点的三大步骤布局规划,定义蚀刻范围的「局部削洗Silicon层的减薄厚度」(milling silicon trench,Max size 350*350um),不过如何提高沟槽(Trench)内表面平整度(参见图二)以及判断终点(End point)位置(参见图三),避免过度蚀刻(Over Etching)(参见图四),将是两大关键技术;以7奈米为例,Silicon厚度保留在1~2微米为最佳(参见图五),这是电路修补前的关键步骤。

图五:晶背电路修补示意图,建议Silicon厚度保留在1~2微米(um)为最佳。

三、 如何精准定位目标、清楚辨识电路

先进工艺,特别是7奈米工艺的金属与介电层的间隙、宽度、厚度,多为40奈米(nm)或以下,面对薄且小的工艺,精准定位目标、清楚辨识电路是最大的挑战,而且电路修补的过程经常是以「秒」来计算,稍一失误将前功尽弃。

该如何精准定位目标呢? 由于从晶背施工,以电子显微镜成像是无法看到线路,需先使用红外线摄影机穿透并依靠四个角落来进行初步定位让GDS对准芯片,再利用一个或多个参考点(reference point),多次定位以降低误差,通常距离目标点最远100微米(um)即可定位,不过越远误差就越高;建议选择距离目标点20微米(um)内,约2*2微米(um) 可破坏区域做为定位点,实际误差可降至150奈米(nm)。

四、 蚀刻参数与气体的调校、避免过曝金属层(Metal)

本文与各位长久以来支持宜特的您,分享经验,若您想要更进一步了解细节,欢迎洽中国免费咨询电话,400-928-9287│ Email: marketing_chn@istgroup.com