发布日期:2022/5/3PCB设计

发布单位:iST宜特

你知道板阶可靠性测试结果是Pass或 Fail,PCB测试板设计居然扮演关键角色?

我们都知道Package设计工程师,来宜特可靠度验证实验室进行板阶可靠性(Board Level Reliability;简称BLR) 测试前,必须先制作PCB测试板,藉此仿真Package组件组装于印刷电路板(Printed Circuit Board;简称PCB)时,可能出现的锡球焊接问题。

在实验过程中,若Package或PCB两者,只要有其中之一失效,可靠度试验就宣告Fail。因此,Package与PCB之间,取得平衡点,才能使实验的寿命优化。

不过在BLR测试中,所需的PCB测试板,本身材料、厚度、走线层面等,不仅须要遵照相关国际规范的要求,更是影响可靠度测试结果的关键。到底,PCB测试板该如何设计,有哪些Know How呢?

PCB设计

一. 如何开始设计PCB测试板

(一) 选择实验欲参照的法规

BLR测试方法可分成五大类,包含热循环 (Thermal Cycling)、振动(Vibration)、落摔(Drop)、循环式弯曲(Cyclic Bending)、静态式弯曲(Static Bending)等测试手法。除热循环(Thermal Cycling)属温变类实验外,其他皆属于机械类别的试验。

板阶可靠性在消费性产品的国际规范可参考 JEDEC B103/ A104/ B111 /B113、IPC-9701~9704/ 9708,或是各家终端消费型品牌大厂,包括手持式产品、车用电子等类型也都有各自定义定的客户规范。而客户BLR测试的依据,可能是基于产业标准或客户标准,故厘清选用的BLR 测试标准是首要之道,再依据其中不同的实验项目选择对应的PCB规范。

不同的实验规范对于PCB测试板的材料参数、厚度、层数、走线层面、铜线宽度,导通孔(Via)设计方式及表面处理等,都有明确定义,某些规范甚至连板层迭构都有要求,因此设计与制作时必须谨慎,避免违反规范。

(二) 准备菊花链(Daisy Chain)的Package与PCB

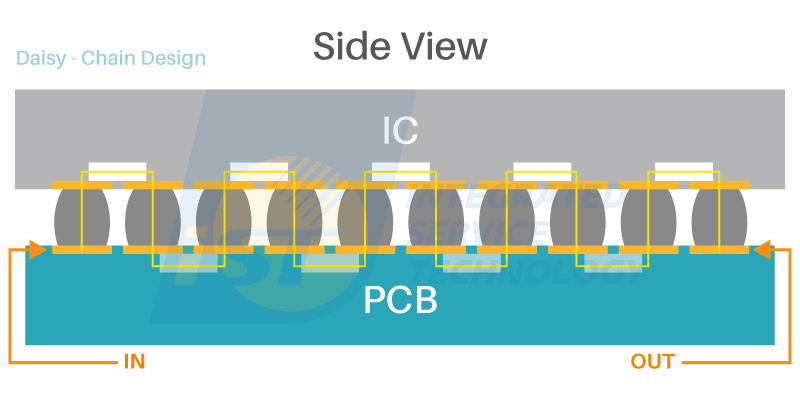

因BLR测试目的是为了解组件上板后的焊点质量,必须透过菊花炼(Daisy Chain)设计,将待测样品组件与电路板链接的各个焊点形成网络,藉此实时监控阻值的变化,可得知各个锡球焊点是否失效,准确撷取失效的时间点,藉此了解各材料所能承受的寿命才可及早进行改善。

- 什么是 Daisy Chain ?

Daisy Chain线路设计可分成两部分,一半的线路是设计在Package组件上,另一半则设计在测试板上,当Package组件透过表面黏着(SMT)到测试板时,即可形成一个完整的Daisy Chain。

图二:Daisy Chain设计

- 什么是 Daisy Chain ?

二. 那些原因将影响BLR中PCB的可靠度?

以下汇整宜特板阶可靠性实验室十多年遇到的状况,可归纳下列七项原因。

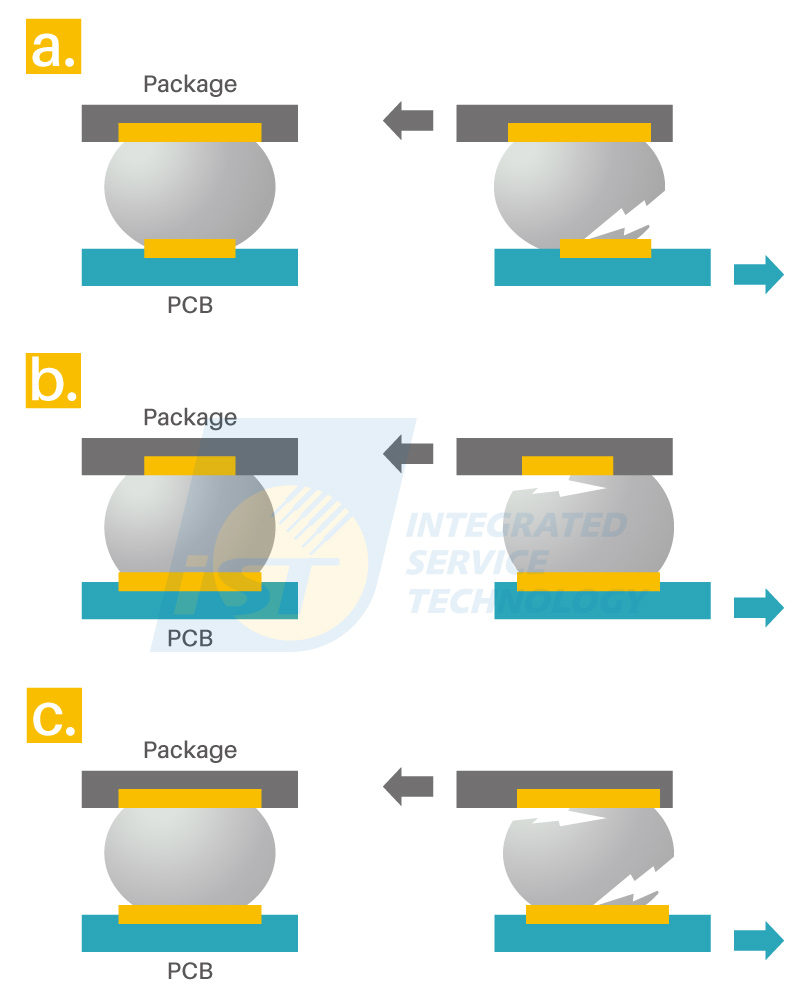

(一) PCB焊垫(Pad)尺寸

试验时所产生的应力,会使Package上板后最弱的位置先裂开。如下图三a.为例,若Package端的焊垫(简称:Pad)尺寸大于PCB端的,则靠近PCB的位置会最早裂开,反之,结果则相反。而当封装与 PCB Pad 尺寸 (图三c.) 一致时,应力分布最均衡,寿命试验数据会较佳。

而为了达成此目标,除了PCB设计时,Pad尺寸需与Package一致外,亦需考虑板厂的制作误差,才能上下均衡,进而延长试验寿命。

图三:PCB Pad 尺寸的影响,其中图a. Package Package的Pad较大,锡球容易在靠近PCB处过早破裂(Crack)。图b. PCB端的Pad较大,导致锡球容易在靠近Package处裂开。图c. 比例则接近一比一,应力是均衡的。虽锡球上下两端都有可能裂开,但完全断裂的时间将被延后。

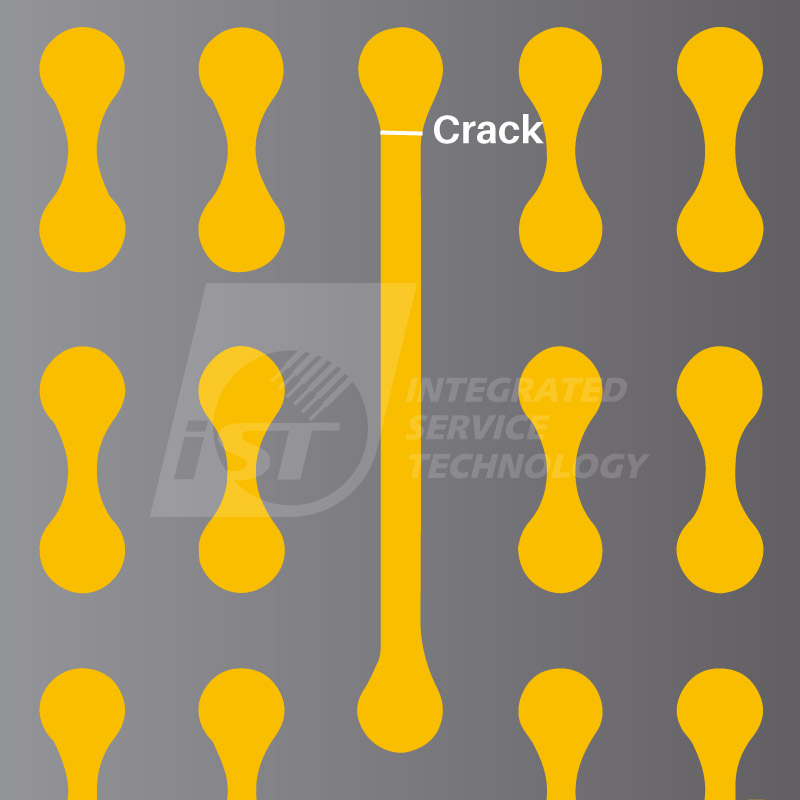

(二) Package Pad分布状况

若Package端Pad有空洞或不规则,应力不平均情况下,就会有Crack风险,如图四裂开Crack位置,最可能发生在缺pad的地方。

图四: Crack情形

(三) 走线层面

不同试验类别,对于走线层面的冲击也不同,必须顺应试验类别选择走线层面。例如,温度循环测试与机械类试验,容易造成Crack的位置就不一样。所以规范IPC9701,要求走线需在表层;而规范IPC9702,则要求走线在内层。

(四) Package size

外型大颗的Package 通常较重,因此不利机械类的实验结果。同时Package基板(Substrate)

也容易在受热后变形 。(五) PCB 翘曲变形

常见造成PCB翘曲变形原因主要有四点,一、须注意板材「热膨胀系数(CTE)」,避免因PCB异

质材料不均匀的收缩,造成严重板翘;二、电路板中各层的「导通孔(Via)」将影响PCB变形幅度; 三、 PCB上Package的「重量」,亦是影响板凹因素,以致SMT后PCB形成哭脸或笑脸,使得锡球变形。四、PCB「铜箔面积不均」,热涨冷缩后造成 PCB 变形。(六) 待测零件摆放至PCB的方向

应以较大应力的方向放置。依据规范JEDEC22-B111、IPC9701要求,Package长短边的摆放方向应与板框一致。

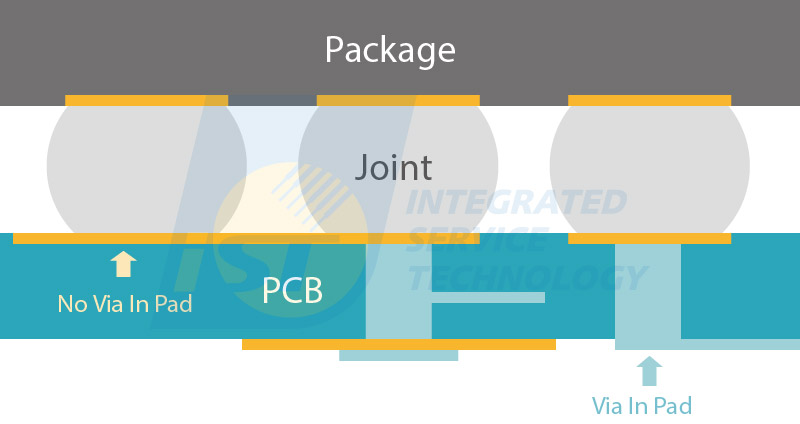

(七) 有无导通孔(Via)

除规范限制外,BGA上,有Via的Pad附着力较好,抵抗整个Pad被拉起的能力,也较无Via优,不过前提是,Via必须电镀回填。

三. 常见客户的疑问

(一) 规范JEDEC 新旧版本该如何选择 ?

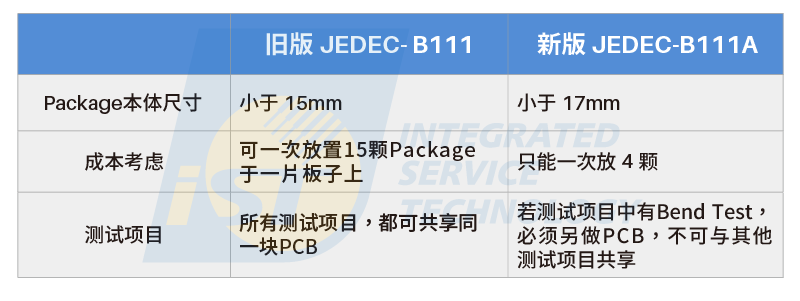

您的产品要遵循旧版本JEDEC- B111或新版本JEDEC-B111A,可从Package本体尺寸、成本、以及试验项目来决定(下表一)。

表一:JDEC新旧版本选择

(二) 是否可于同一片PCB置具放置不同的package?

答案是不行的,不同的Package尺寸不可混合在同一块板上,因为会影响板子的动态响应,造成结果难以分析。

(三) 不同实验是否可共享 PCB测试板?

不同试验是否可共享同一块PCB?例如IPC 9701 TCT与IPC9702 Bend 是否可共享? 宜特板阶可靠性验证实验室的实务经验中,是「不建议」共享,因不同实验参照的法规不同,所以在PCB的零件摆放位置、板厚,甚至走线层面等都各有要求,若共享 PCB,将可能导致试验提早发生失效。

(四) Daisy chain 要怎么设计最好呢?

最常见的Daisy Chain,是依据Pad的分布位置区分为不同的Channel,有助于失效侦测及异常分析。

- 可分为一个或多个Daisy Chain进行监测。依PAD分布位置区分为不同的Channel。

- 每个Daisy Chain的输入和输出端都必须连接到Connector Pin。

- 封装上的所有焊点都应被Daisy Chain所覆盖,包括Ground & Power Pin。

- 尽量增加测试点,提供异常发生时的故障分析(FA)需求。

本文与各位长久以来支持宜特的您,分享BLR PCB经验,若您想要进一步了解如何根据规范进行PCB测试板制作,请回信给宜特,宜特将手刀奉上一张由宜特精心制作的图表,让你一目了然国际规范。请洽+886-3-579-9909 分机 6480 林小姐,Email: web_rce@istgroup.com 或marketing_tw@istgroup.com