发布日期:2022/6/28先进封装焊点异常

发布单位:iST宜特

板阶可靠性试验结果Fail了,长官要你Debug,

如何使用简单三步骤,快速找到异常位置呢?

板阶可靠性(Board Level Reliability,简称BLR )是国际上常用来验证焊点强度的实验手法,透过将仿真组件组装于PCB,重现出可能会发生的锡球焊接问题

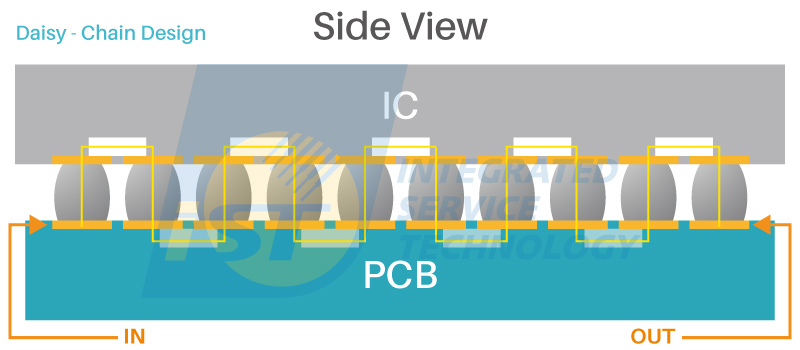

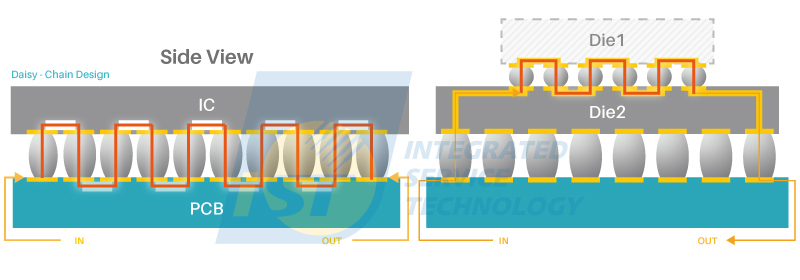

BLR的第一步,需要先进行菊花炼(Daisy Chain)设计,将您的待测样品组件与电路板链接的各个焊点形成网络,藉此实时监控每个焊点良率,可成功得知各个锡球焊点是否失效,更能准确撷取失效的时间点,及早进行改善。

先进封装焊点异常

一、一般封装样品,利用二分法进行走线电性测试

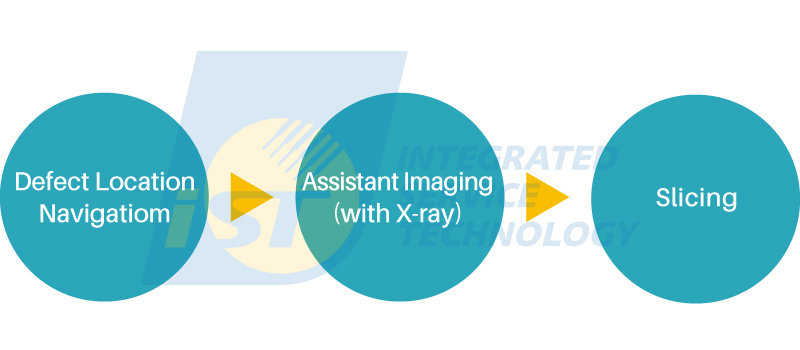

在完成板阶可靠度试验后,若实验后仍保有电性(Leakage/Short),第一步骤,宜特实验室会先使用如Thermal EMMI(InSb)电性热点(Hot Spot)测试机台,定位故障点XY坐标位置。第二步骤,利用非破坏式的X-Ray/3D X-Ray显像。第三步骤,可选择使用较低应力的Plasma-FIB,或是使用研磨(Cross-section polish)搭配SEM的方式,将失效断面切出并分析真因。

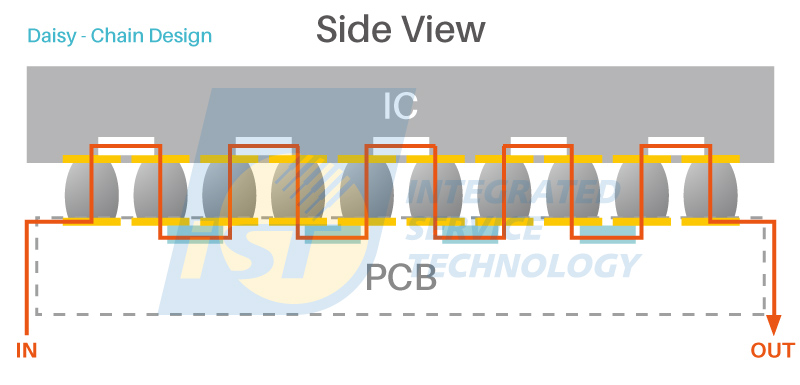

若异常现象为「开路(Open)现象」,因Open已无电流流过,无法使用热点分析定位异常位置。必须在第一步骤「定位」前,先将样品进行破坏性的水平研磨制备,从PCB测试板端水平研磨至Daisy Chain走线裸露后(图三),接着,透过「二分法」(图四),进行走线的电性测试,找到异常的相对位置(定位)。

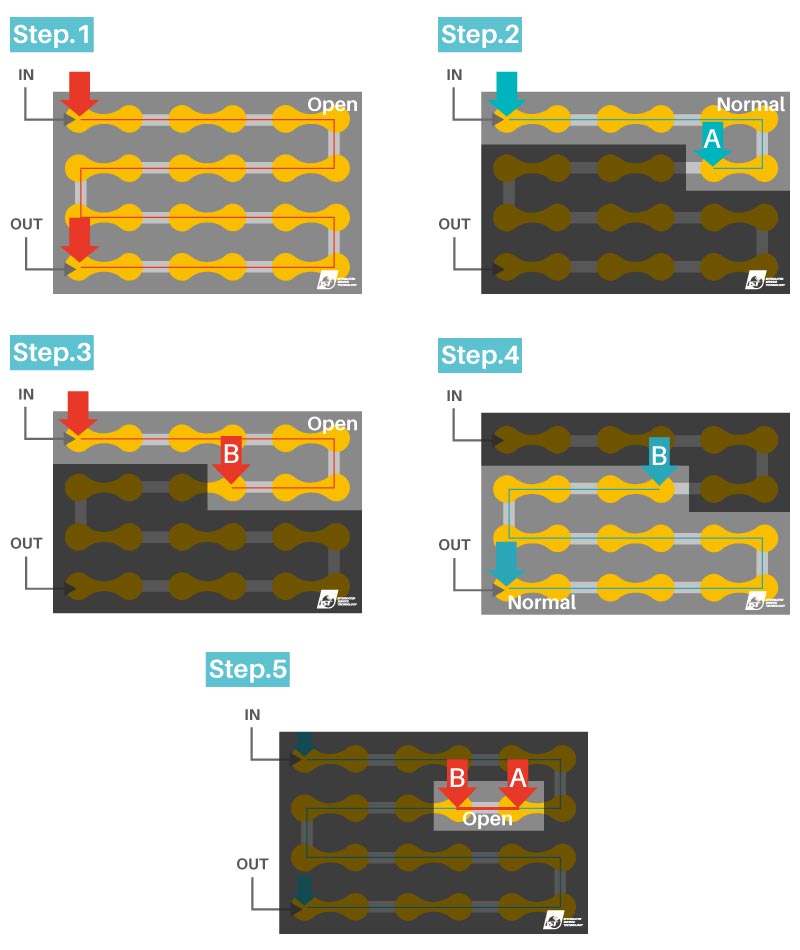

图四:透过二分法,进行走线电性测试,一步步找到异常相对位置:图四(1),先在IN与OUT点通电,发现Open(异常)。接着,图四(2)在IN与A点通电,电性正常。接着,图四(3),在IN与B点通电,显示Open(异常)。图四(4),在OUT与B点通电,电性正常。最后图四(5),在B与A点通电,显示Open(异常);藉由二分法,找到异常相对位置。

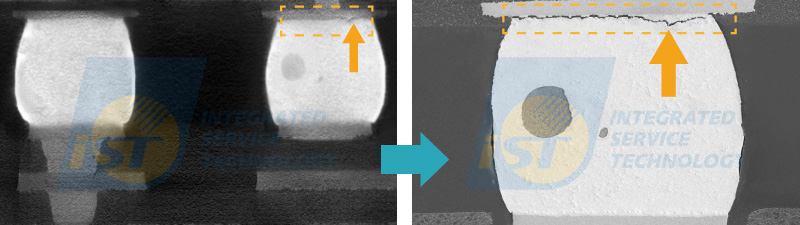

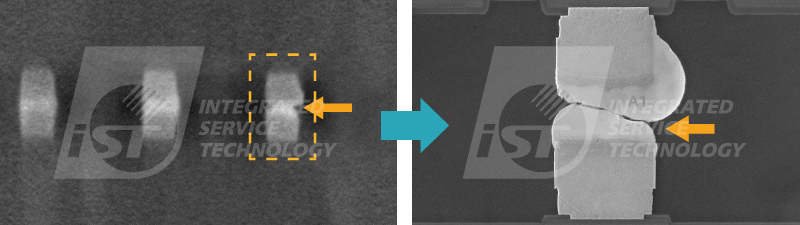

第二步骤,透过X-Ray收敛异常点,从图五(左)中,我们可以清楚看见锡球与焊垫(Pad)连接的地方,出现异常(显像)。第三步骤,切片进一步观察,从图五(右)中,则发现锡球裂开了,就此找到发生阻值异常的原因(切片)。

二、先进封装样品,透过EBAC,找到异常断点

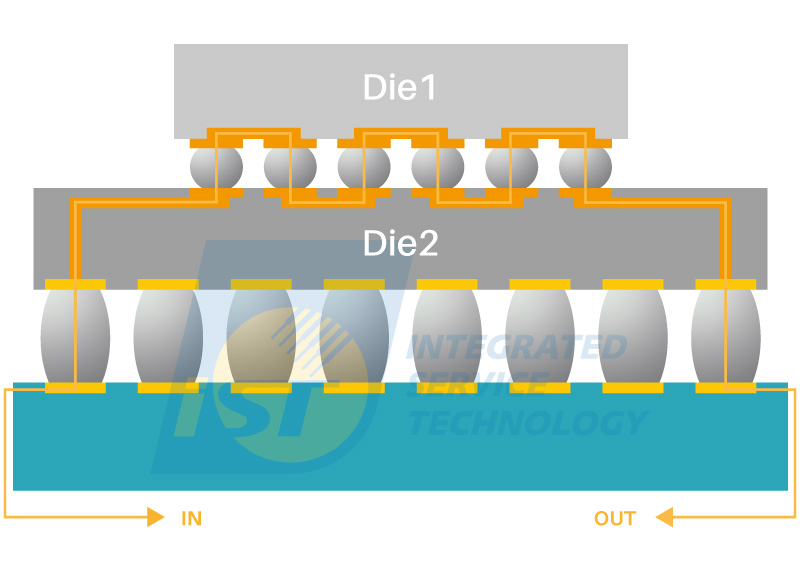

若是像2.5D或3D IC等先进封装样品,封装形式属多芯片, Daisy Chain的设计,将跳脱以往单一芯片搭配一个测试板,而是多芯片搭配在一个测试板的形式(图六),那么板阶可靠度试验后出现故障后,该如何找异常点呢?

若异常型态为仍有电性(Short/Leakage),可用同一般封装样品故障分析形式,先使用Thermal EMMI(InSb)进行热点分析,定位异常位置,并透过X-Ray/3D X-ray显像,最后使用Plasma FIB物性研磨,将失效断面切出进行分析。

若异常型态为「Open」,一样同一般封装形式,必须在「定位」前,先进行样品制备。不过,这边要特别留意,一般封装形式Daisy Chain走线是位在IC与PCB板间(参见图七(左)),但先进封装形式,Daisy Chain走线路径则介于两颗Die之间(参见图七(右)),因此无法使用从PCB测试板端研磨的传统方式(走线不在PCB端),就必须从晶背端,利用干式蚀刻方式,让位于Die 1与Die 2间的Daisy Chain走线裸露。

图七(左):一般封装形式,Daisy Chain走线位于PCB与IC间;图七(右):先进封装形式,Daisy Chain走线位于Die 1与Die2间,透过干式蚀刻,使Die 1的 Daisy Chain走线裸露。

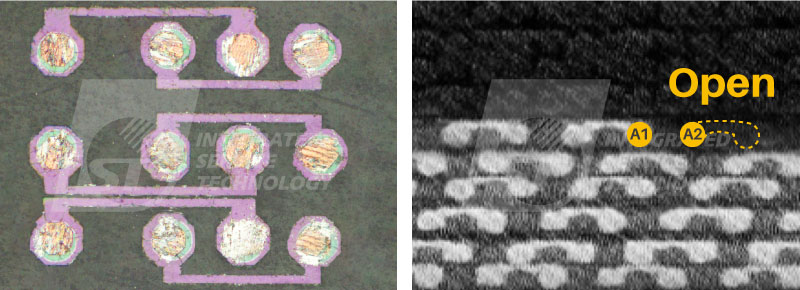

Daisy Chain裸露后(图八(左)),我们即可进行第一步骤「定位」,因此时异常情况为Open,无法通电,就无法使用Thermal EMMI(InSb)定位Hot Spot,必须透过EBAC,将电子束导入样品内部,电荷会累积于正常走线处,而异常处电荷无法累积,画面就会全暗,即可判别异常位置,找到异常断点(图八(右))。

第二步骤「显像」,安排X-ray/3D X-ray复检,发现锡球接合异常(图九(左))。第三步骤「切片」,安排Plasma FIB/物性研磨进行切片,找到异常现象为锡球断裂(图九(右))。

本篇宜特小学堂,特别提供给长久以来支持我们的客户,若您对此实验手法有兴趣或有任何需求, 或是对相关知识想要更进一步了解细节,欢迎洽询 +886-3-579-9909 分机 6757 杨小姐 │ Email: web_ise@istgroup.com, marketing_tw@istgroup.com